### Washington University School of Medicine

### Digital Commons@Becker

**Technical Reports**

Institute for Biomedical Computing

2-1974

# Macromodules Computer Design, Part 1, Volume 1, Overview of Macromodules

Computer Systems Laboratory, Washington University

Follow this and additional works at: https://digitalcommons.wustl.edu/bcl\_techreports

### **Recommended Citation**

"Macromodular Computer Design, Part 1, Volume 1, Overview of Macromodules," Computer Systems Laboratory, Washington University (1974). *Technical Reports*. Paper 1. https://digitalcommons.wustl.edu/bcl\_techreports/1

This Technical Report is brought to you for free and open access by the Institute for Biomedical Computing at Digital Commons@Becker. It has been accepted for inclusion in Technical Reports by an authorized administrator of Digital Commons@Becker. For more information, please contact vanam@wustl.edu.

# MACROMODULAR COMPUTER DESIGN PART 1. DEVELOPMENT OF MACROMODULES

VOLUME I

OVERVIEW OF MACROMODULES

Technical Report No. 44

FINAL REPORT - FEBRUARY, 1974

CONTRACT SD-302 (ARPA)

COMPUTER SYSTEMS, LABORATORY

WASHINGTON UNIVERSITY

ST. LOUIS, MISSOURI

### MACROMODULAR COMPUTER DESIGN

FINAL REPORT - CONTRACT SD-302

FEBRUARY, 1974

## Technical Report No. 44

PART 1 - DEVELOPMENT OF MACROMODULES

VOL. I - OVERVIEW OF MACROMODULES

This work has been supported by the Advanced Research Projects Agency of the Department of Defense under Contract SD-302 and by the Division of Research Facilities and Resources of the National Institutes of Health under Grant RR-00396.

The views and conclusions contained in this document are those of the authors and should not be interpreted as necessarily representing the official policies, either expressed or implied, of the Advanced Research Projects Agency or the U.S. Government.

Computer Systems Laboratory Washington University St. Louis, Missouri

### ABSTRACT

This volume contains a Foreword to the Final Report, two excerpted reprints that present the initial conception of macromodules and means for implementing them as seen in the early days of the project, and a third reprinted report that presents a summary and overview as of the autumn of 1972.

### FOREWORD TO FINAL REPORT

This set of documents represents an attempt to bring together in one place sufficient material to enable the reader to obtain a reasonable overview of the major ideas and conceptions that gave rise to the macromodule development project at Washington University, and to report and record some of the details of the ensuing development effort and its results. Since the project is continuing with other support past the termination of the contract for which this is the final report, certain aspects of this report deal with efforts that are still in progress, particularly the design of restructured macromodules and the use of macromodules as a tool for technological and scientific research.

Part 1 of this report deals with the development of Phase I macromodules, of which over 800 modules of 17 types have been constructed and made part of a working inventory that resides at Washington University. This volume contains two excerpted reprints that present the initial conception of macromodules and means for implementing them as seen in the early days of the project, and a third reprinted report that presents a summary and overview as of the autumn of 1972. Further details of the functional definition and design of macromodules are presented in the remainder of Part 1.

The second Part of this report contains detailed manufacturing descriptions of macromodular parts and assemblies; it is based directly upon documents used to carry out the fabrication. This highly detailed material is intended to serve as a reference for those wishing to understand more thoroughly the material that is presented in Part 1, and may also contain useful ideas for other designers.

A status report on restructured macromodules makes up the single volume of Part 3 of this Report. Some of our judgments based upon our experience with Phase I macromodules are also reflected in that volume.

It should be pointed out that in addition to this report, there are numerous other documents dealing with particular aspects of the macromodular design project. These include a series of formal Technical Reports of the Computer Systems Laboratory, and an informal series of Technical Memoranda that were primarily intended for internal use and record purposes but contain substantial information of possible broader interest. Relevant documents of these series, as well as a bibliography of relevant publications in the open literature, are listed in Volume V of Part 1. Copies of relevant Technical Reports have been supplied to the Defense Documentation Center and should be available through their channels.

There is no adequate way to acknowledge and summarize the diverse and often intense interactions of people and ideas that have taken place during this project, and the precise roles and contributions of the participants in this large effort were often unclear at times even to the individuals who were directly involved. At this time it appears impractical to improve upon the

acknowledgements that may be found in the reprinted articles contained in this volume, and a comprehensive but undifferentiated list of persons associated with the project since its inception is included in Volume V of Part 1. It is my sincere hope that their participation in this large effort will prove to have been as beneficial to them as it has to the progress of macromodular design.

Charles E. Molnar

Director

Computer Systems Laboratory

Washington University

### A MACROMODULAR APPROACH TO COMPUTER DESIGN

A Preliminary Report

(reprinted here in its entirety)

Wesley A. Clark

Mishell J. Stucki

Severo M. Ornstein

Technical Report No. 1 February 21, 1966

Computer Research Laboratory

Washington University

700 South Euclid Avenue

St. Louis, Missouri

This work has been supported by the Advanced Research Projects Agency of the Department of Defense under contract SD-302 and by the Division of Research Facilities and Resources of the National Institutes of Health under grant FR-00218.

### INTRODUCTION

The amount of logically irrelevant engineering detail inherent in the design and construction of a computer system is great. As a result, the task of creating a system based on the use of present techniques is so difficult and time-consuming that the number of different systems that can be put into use for evaluation and study by any one group of workers is small. This is unfortunate as we are thereby denied the opportunity to develop that insight into logical organization which can grow out of a working familiarity with many diverse forms. What is needed is a set of relatively simple, easily inter-connected modules from which working systems can readily be assembled for evaluation and study. With such a set, both the designer and user would be able to try out potentially powerful and novel structures on a very large scale, adjusting and improving the systems as needed. Once a design has been realized and its value established, it could then be reworked into tighter engineering form for maximum efficiency and for production by automatic wiring and fabrication techniques, and the experimental units made available for further studies or returned to "inventory" in the manner proposed by Estrin .

The modules as described are primarily vehicles for experimental use and as such must meet a set of requirements heretofore unnecessary in digital modules. Logical flexibility and ease of use must be considered of primary importance while factors such as operating speed, economy, etc., though not ignored, must be considered of secondary importance. The requirements can be summarized as follows:

1) The modules must be functionally large enough to reduce logical detail by a significant amount and must be relatively easy to understand and assemble. The number of different types should be small as possible so as to limit inventory, but at the same time, the set must be logically complete so that whole systems may be assembled. There must be not only central processor modules such as register and memory units, but also modules for power, signal conditioning,

input-output buffering and control, together with a reasonable selection of input-output devices themselves.

- 2) The mode of combining units into larger structures must be very simple (a problem first considered by Babbage, who examined this matter "with unceasing anxiety" one hundred and twenty years ago<sup>2</sup>). The modules should be designed for easy mechanical assembly. Communication from one mechanical assemblage to another should be accomplished by means of easily connected cables.

- 3) All units should be designed so that the assembling of these units into a working system presents no logically irrelevant problems such as those relating to circuit loading, waveform deterioration, signal propagation delay, power supply interactions, and so forth, regardless of the size or complexity of the system. The modules should be powered and perhaps cooled individually, and all possible signal paths must be provided with signal-standardizing amplifiers capable of driving all possible loads.

We call units which meet these requirements <u>macromodules</u> to distinguish them from the more conventional computer system modules. In this report we present a set of macromodules which, although not "complete" in the above sense, meets all other requirements and is sufficient for the synthesis of all central processor functions of which we are presently aware. Particular attention is given to the problem of control structures and a technique is presented in which the control signals for a given process are routed along a control network whose topology is isomorphic to the flow diagram representing the process. The step from conceptualization to realization can therefore be made directly, a situation that enormously simplifies design.

### MACROMODULAR SYSTEMS

### General Characteristics

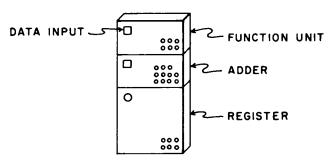

The macromodules to be described are relatively small, dimensionally modular, structurally self-sufficient boxes which contain all of the required electronic circuits and memory elements. Electrical connectors on the faces of each unit provide all power and signal access. The units can be interconnected mechanically and electrically to form larger assemblages, and standardized cables are provided for all inter-assemblage communication. All connectors are backed by signal-standardizing amplifiers capable of driving any attachable module or cable.

Data processing modules are organized in parallel binary form with a word-length modulus of 12 bits, and are designed functionally for asynchronous operation. Memory modules hold 4096 12-bit words.\*

The design of a system based on these modules requires, we believe, only the exercise of logic. The operability of the resulting system cannot be adversely affected by the physical distribution or arrangement of parts, the distances between units, the number or diversity of modules, or the routing of the interconnecting pathways. Macromodular systems are, as a result, capable of continuous growth and functional enrichment.

<sup>\*</sup> The numbers 12, 4096, and other such parameters have been made specific, for purposes of this report, only to simplify description.

### System Organization

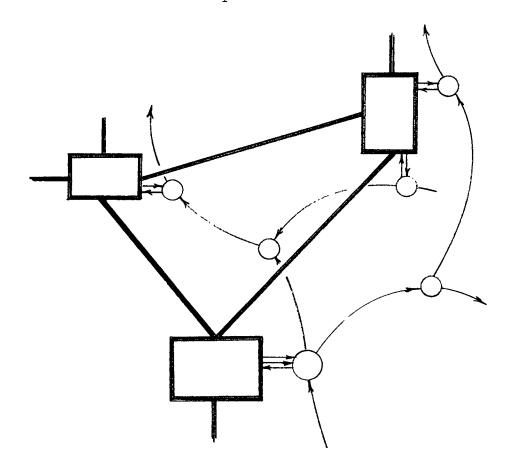

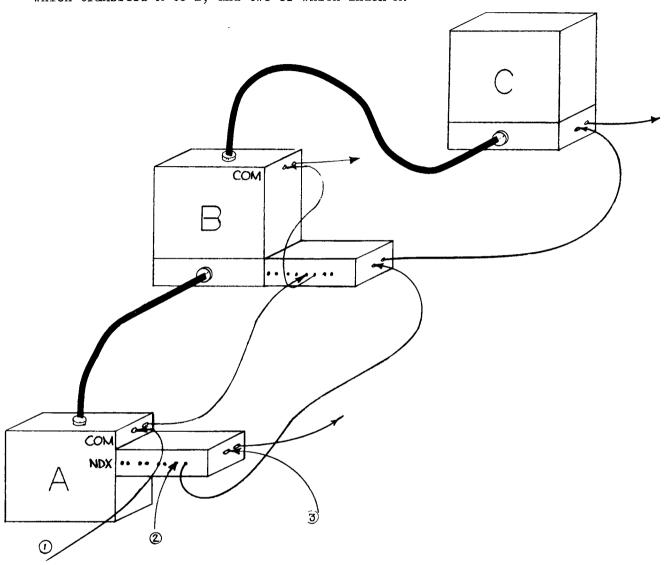

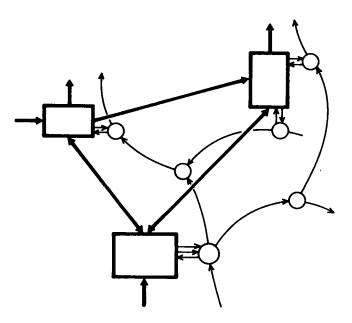

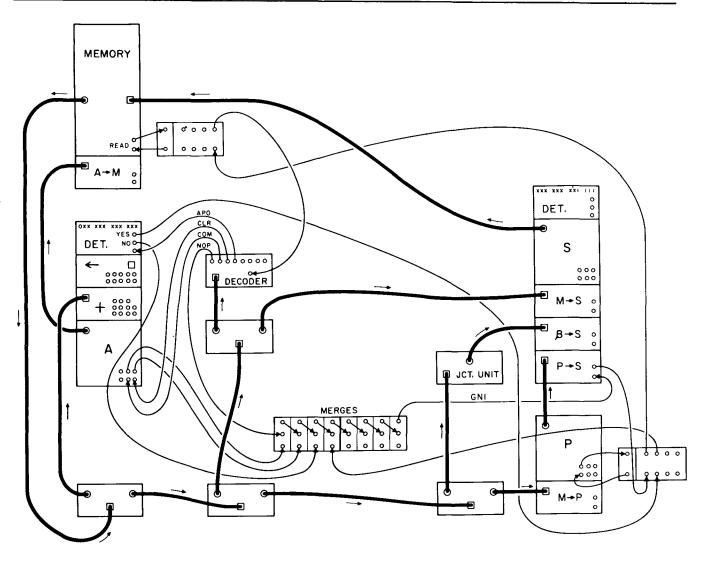

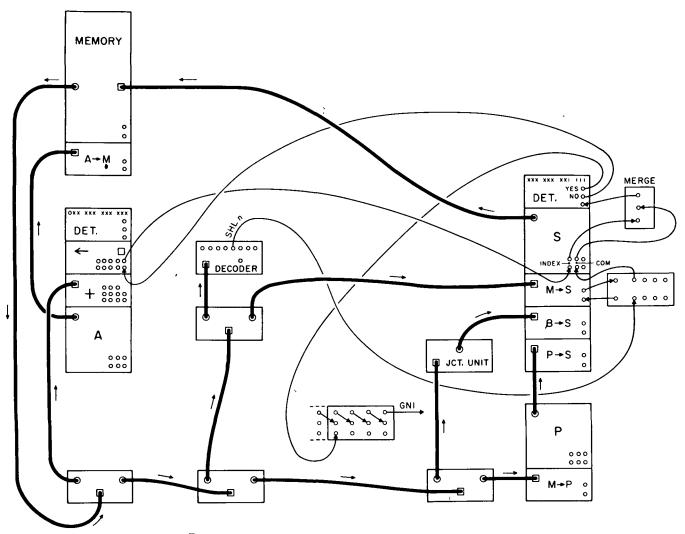

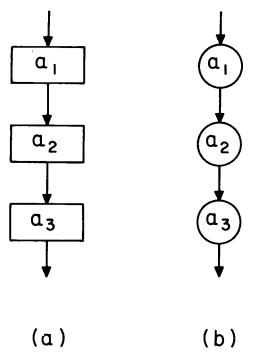

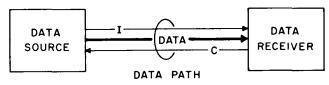

Macromodular systems may be viewed in terms of two logically distinct, interacting networks (Fig. 1). The <u>Processing Network</u> (the heavy-lined structure) consists of data processing elements interconnected by data pathways, and provides for the storage, propagation, and transformation of data within a system. The <u>Sequencing Network</u> (the light-lined structure) consists of control nodes distributed throughout the system, interconnected by control pathways. The structure of the Processing Network defines the basic data processing operations of the system while the structure of the Sequencing Network defines the order in which subsets of these basic operations can be carried out.

Fig. 1

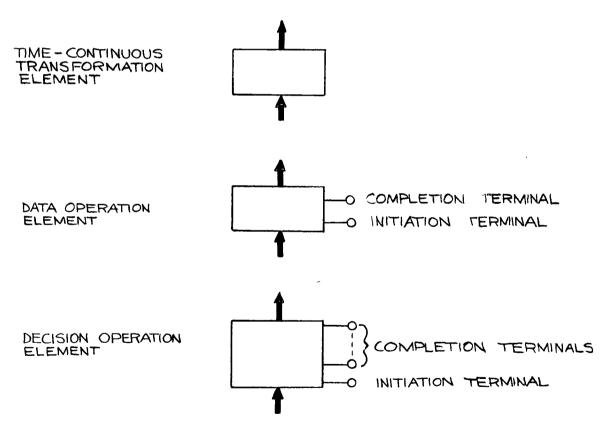

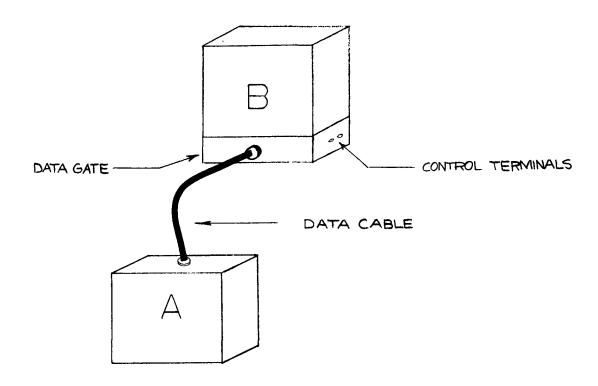

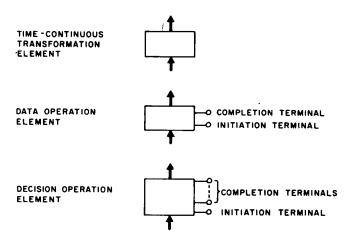

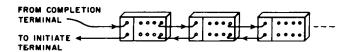

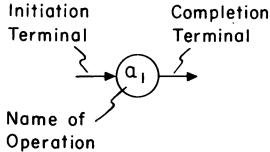

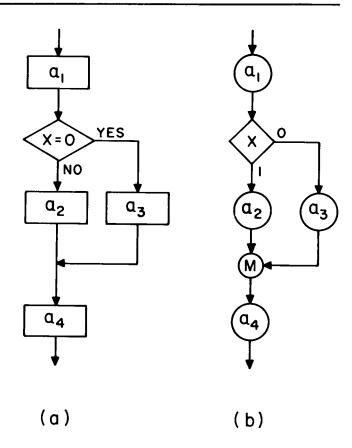

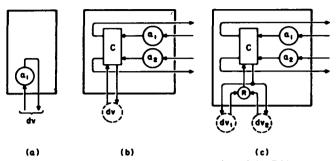

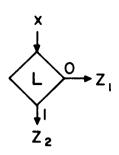

Interaction between these networks takes place at control terminals on the data processing elements. These terminals have two functions: they allow the Sequencing Network to initiate operations, and they return completion signals when the operations are finished. Each basic data processing operation has an associated set of these terminals (Fig. 2), the number of terminals in the set being determined by the nature of the operation. Operations that manipulate data, data operations, have two, an initiation terminal and a completion terminal. Operations that check data for specific values, decision operations, have more than two, one to initiate the operation and the others (completion terminals) to indicate the value of the data found. Also shown in Fig. 2 is a time-continuous transformation element. This element, unlike those already described, performs its operation continuously. The data presented at its output changes only in response to changes of input data rather than in response to control signals, and as a result, the element has no control terminals at all.

Fig. 2

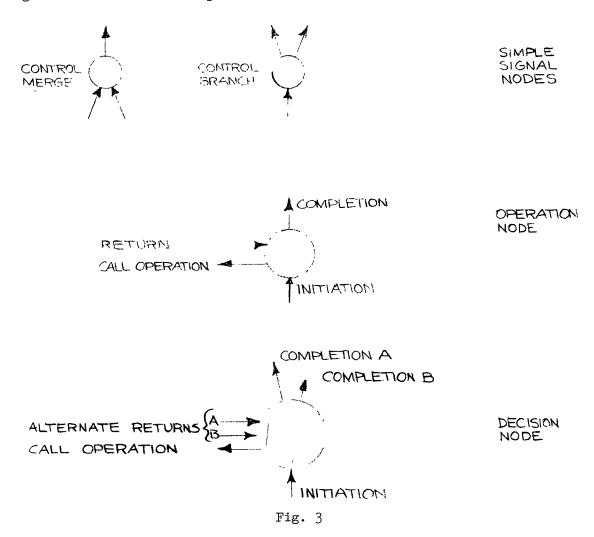

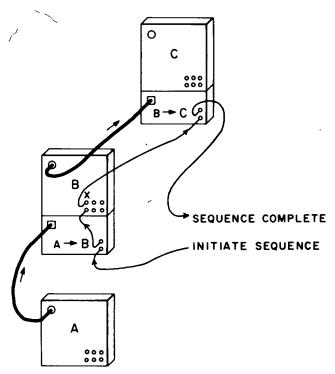

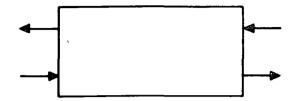

The order or sequence in which operations are performed is determined entirely by the structure of the Sequencing Network. This network is composed of signal nodes, calling elements, and interconnecting pathways.

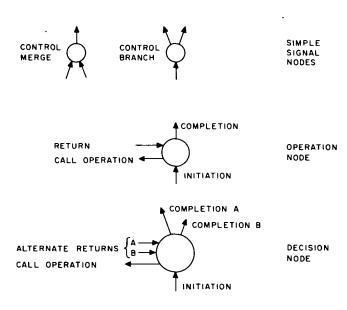

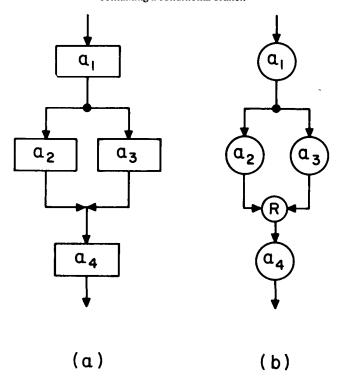

A signal node is an element which provides for the merging or branching of control signals. There are several types, two of which are shown in Fig. 3. A calling element is one which, when activated by a control signal on its initiation terminal, causes an operation to take place and, when signaled of its completion, produces its own completion signal in turn. An operation node is a calling element for data operations, and a decision node is a calling element for decision operations.

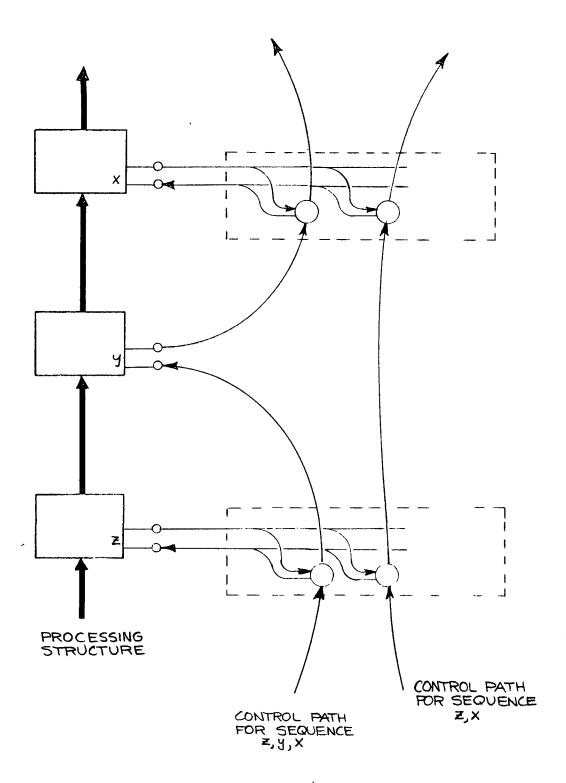

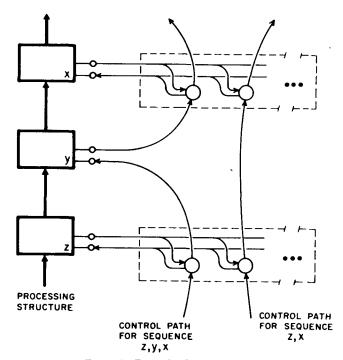

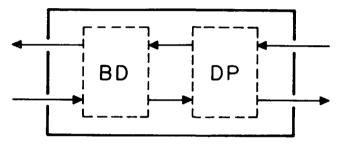

Control within a macromodular system is asynchronous, that is, each event in a sequence of events is initiated by the completion signal from the preceding event. The simplest way of arranging for this would be to connect the completion terminal associated with each operation to the initiation terminal associated with the next operation. This scheme, though simple and effective, does have the limitation, however, that once the control terminals for an operation have been connected for one sequence, it is no longer possible to incorporate the operation into any other sequence. We therefore revise the scheme as follows: rather than connect to the terminals associated with the operation, we connect instead to the terminals of a calling element associated with the operation, as shown in figure 4. Since any number of calling elements may call the same operation, an operation may now occur in as many sequences as necessary. Figure 4 illustrates this for two different sequences, sequence z, y, x and sequence z, x. Since both sequences include the operations z and x, they initiate the operations via calling elements. Calling elements are not needed for operation y, however, as it appears in only one sequence and can therefore be incorporated by connections directly to its control terminals.

Fig. 4

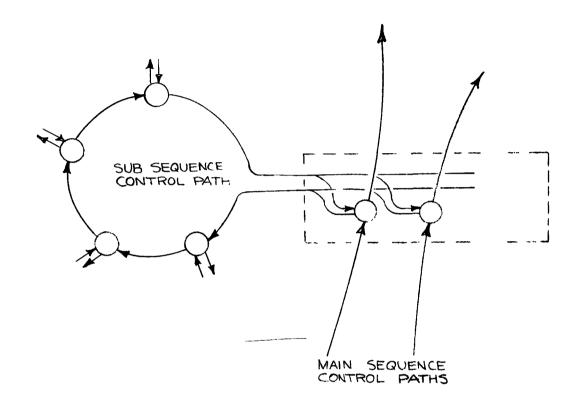

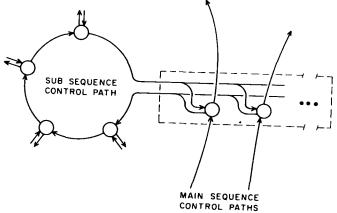

The control structure described above has the additional feature that an entire sub-sequence of operations can be called by a calling element (Fig. 5). This allows sequences to share common sub-sequences, thereby reducing the number of control elements and interconnections required in a system.

Fig. 5

The control elements and interconnections that define a given sequence are said to be the  $\underline{\text{control}}$   $\underline{\text{path}}$  for that sequence. The Sequencing Network is therefore the control  $\underline{\text{path}}$  for the entire system.

### Data Validation

In order to perform an operation on data or make a decision based on the value of data, it must first be established that the data is available at the point at which it is to be used. There are two general requirements to be met:

- 1) The data source must present the data in stable form, that is, it must have completed any operation initiated earlier which may affect the data. This requirement stems from the fact that, in the interest of speed, a data element generates a completion signal as soon as it no longer relies upon its input data, regardless of whether or not its operation is complete and its outputs stabilized.

- 2) Enough time must be allowed for the stable data signals to propagate to the point of use regardless of the length of the pathway.

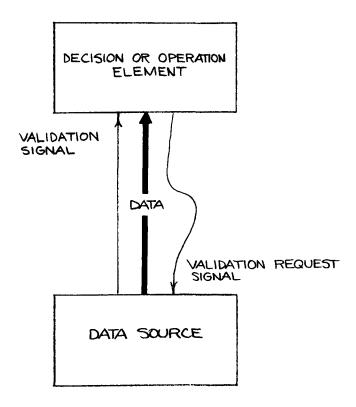

When data is used in the immediate locality of its source, i.e., within the same data processing element, allowances for stabilization and propagation times are made by the element itself. When the source is remote from the point of use, a procedure known as <u>Data Validation</u> (Fig. 6) is used to guarantee that the requirements are met.

Fig. 6

In this process, before data from a remote source is used, a <u>Validation Request Signal</u> is transmitted to the module containing the data. In response, that module generates a <u>Validation Signal</u> as soon as the signals on its data output terminals are stable. This signal travels back to the point at which the data is to be used along a pathway exactly parallel\* to the data pathway, thereby providing time for data propagation along that pathway regardless of its length. The signal is made to travel somewhat slower than the data so that when it arrives at the point of use, the data is guaranteed to meet both of the above requirements and can be used immediately.

<sup>\*</sup> The data Validation Signal travels on a special channel in the same cable that carries the data thus insuring that its path is exactly parallel to that traveled by the data. For simplicity, the Validation Request Signal also travels on another channel of the data cable.

### THE MACROMODULES

We now proceed to give a functional description of the individual macromodules and illustrate their roles in various systems. Processing Network elements are introduced first, and this is followed by a discussion of the various Sequencing Network elements. Power connections are omitted from all figures to avoid obscuring the logical point being illustrated.

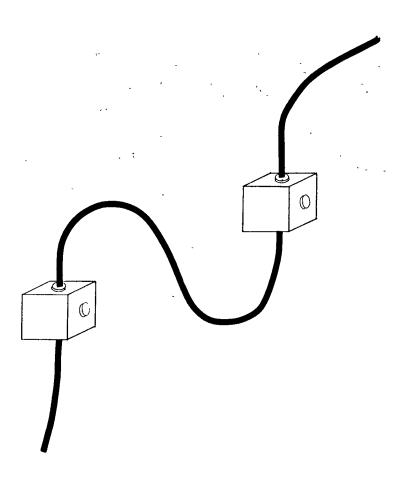

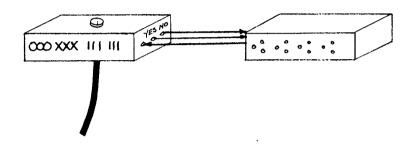

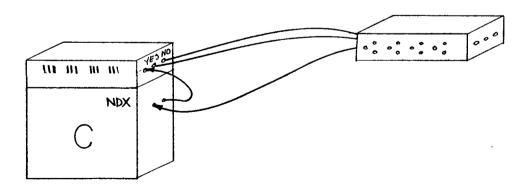

### Cables

Data paths are constructed with <u>Data Cables</u>, control paths with <u>Control Cables</u>. These cables are made in a limited number of lengths, but cables of any length can be formed by using signal-standardizing extender units. A Control Cable contains a single channel for transmission of a control signal. A Data Cable contains 14 channels, 12 for the transmission of data and one each for the Validation Request Signal and the Validation Signal. In the illustrations, Data Cables are drawn with heavy lines and Control Cables are drawn with thin lines.

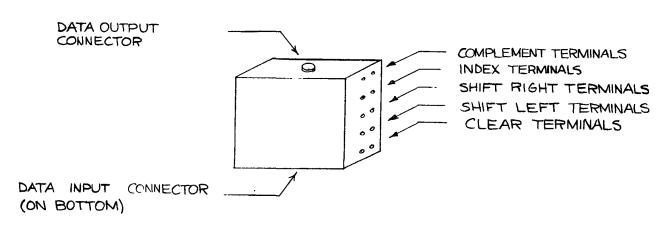

### Registers

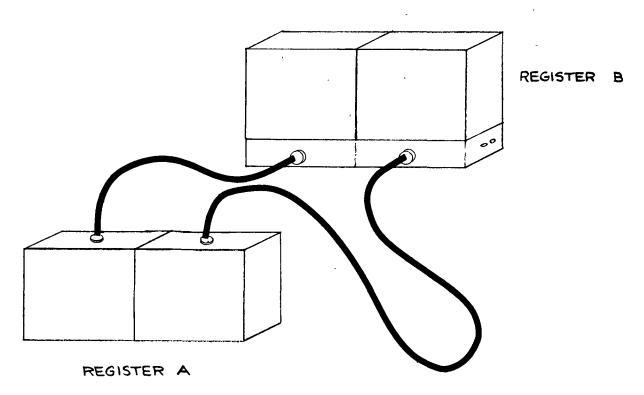

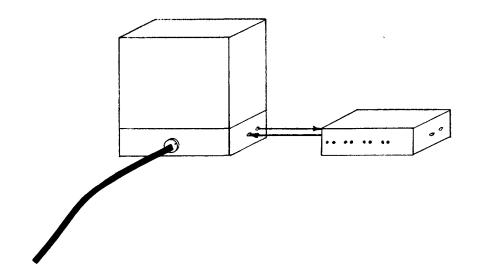

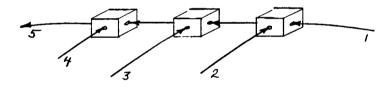

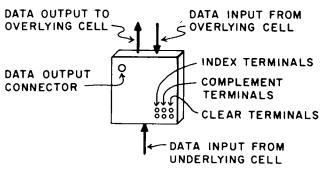

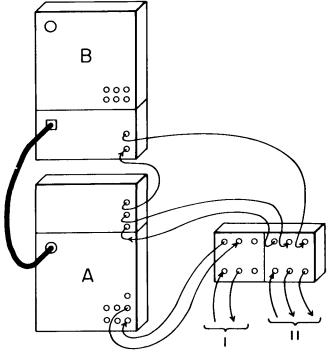

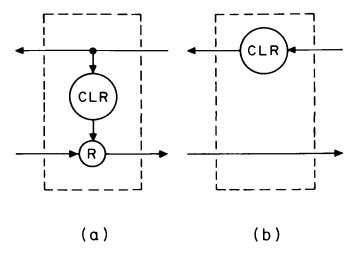

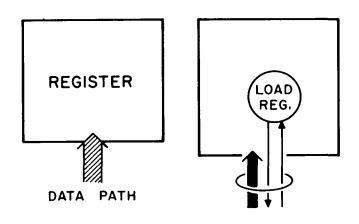

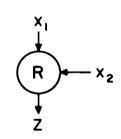

The basic Register Module (Fig. 7) contains a 12-bit register together with logic for the operations <u>clear</u>, <u>complement</u>, <u>shift left</u>, <u>shift right</u>, and <u>count (index)</u> Control terminals for each operation are mounted on one side of the module, and connectors on the bottom and top provide for input and output of data.

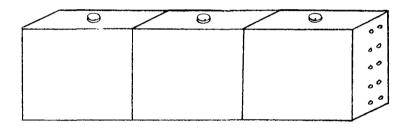

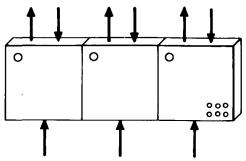

Registers of any length can be formed by plugging these modules together, lateral pathways being joined by interface connectors (not shown in the figures). Figure 8 shows a 36-bit register formed from three Register Modules. Plugging the modules together obscures the control terminals on all but the rightmost module so that the resulting register has but one set of control terminals, and these provide for the control of the whole register. This is particularly important as it makes control of an operation independent of register size. When modules are plugged together, special circuits within each module are coupled in such a way as to compensate automatically for the increased lateral signal propagation times. Proper operation is thereby guaranteed regardless of register length.

Fig. 8

### Transfer Operations

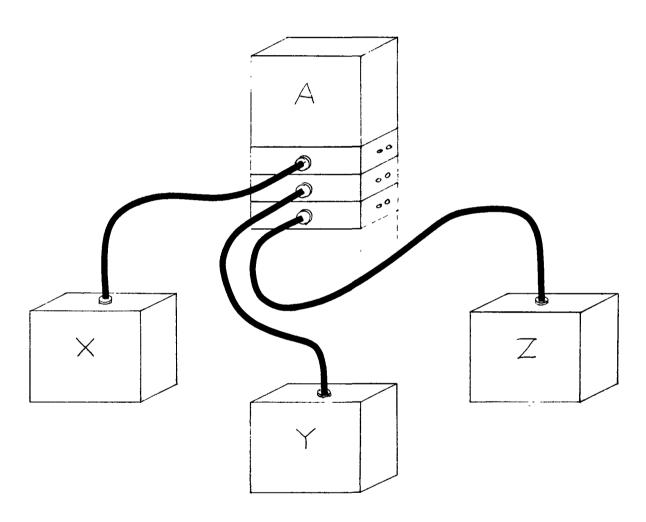

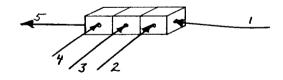

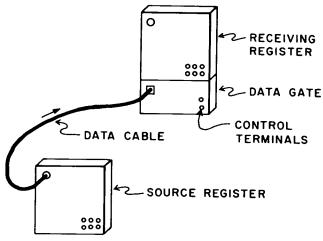

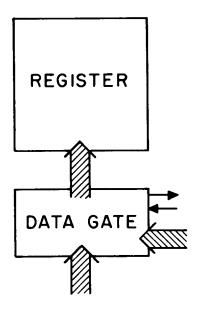

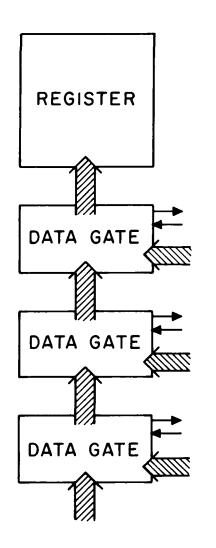

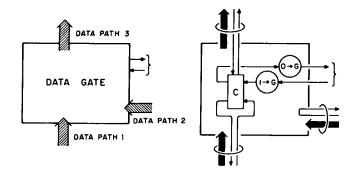

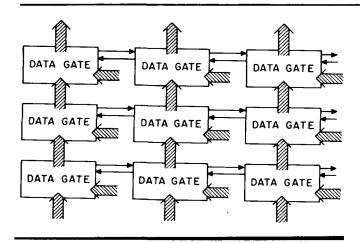

Data transfers from one Register Module to another require the use of a <u>Data Gate</u> module. This unit plugs directly into the base of the receiving Register Module and is connected by means of a Data Cable to the output of the data source Register Module (Fig. 9). Twelve bits are transferred in parallel, and the transfer initiation and completion terminals appear on one side of the module. Transfers are <u>copying</u> operations and as such do not alter the information at the source.

Fig. 9

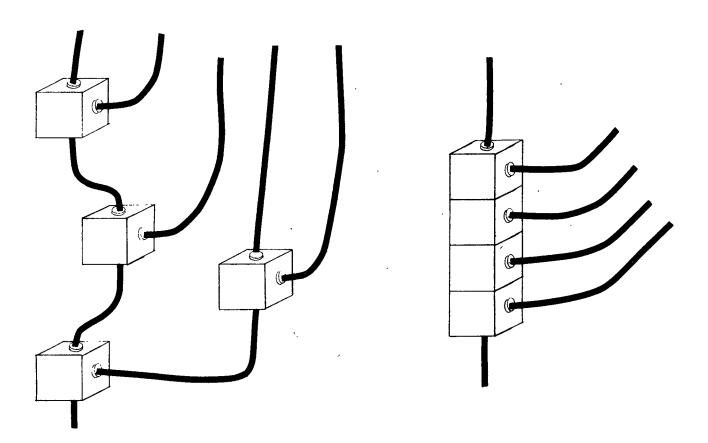

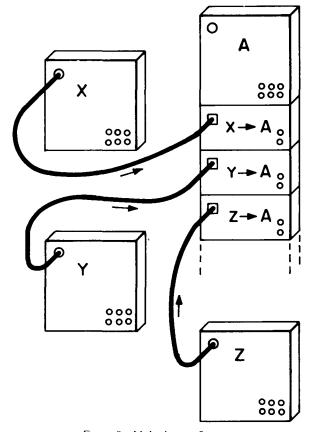

A separate Data Gate is required for every transfer path into a Register Module. If, therefore, a Register Module is to receive input from n other Register Modules, n Data Gates are required. Figure 10 shows a Register Module equipped with transfer paths from three other Modules. Note that only one of the Data Gates plugs into the Register Module itself; each of the others plugs into the base of another Data Gate. Stacking the units in this way allows each Data Gate to communicate with the receiving Register Module. Any number of transfer paths into a Register Module can be provided by stacking an appropriate number of Data Gates in this manner.

Fig. 10

To transfer information, data must be gated onto bus lines passing through the Data Gates which go up into the Register Module. It is important to consider the action of a Data Gate somewhere in the middle of a stack of Data Gates attached to a Register Module. When a particular Data Gate receives a control signal at its initiation terminal, it performs a data validity check as described previously. This establishes the validity of the data signals at the Data Gate itself. Because of stacking, however, the Register Module must be considered to be an arbitrary distance, and therefore time, away from the Data Gate. Hence, after the Validation Signal arrives at the Data Gate, it is transmitted up into the Register Module along a pathway parallel to but slower than that travelled by the data to the Module. It thus arrives at the Register Module slightly later than the gated data which can therefore immediately be transferred into the register. A completion signal, indicating that the transfer has been accomplished, is then returned down through the stack to exit at the active Data Gate's completion terminal.

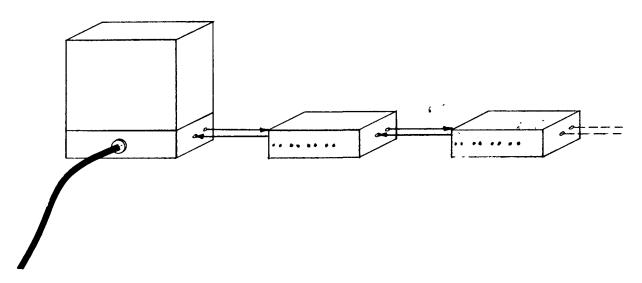

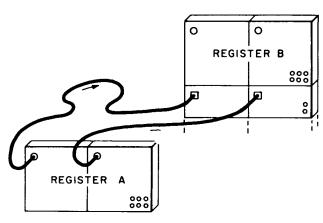

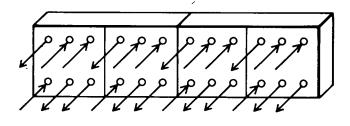

Data Gates can be plugged together to provide for transfers into longer registers. The resulting combination has but one set of control terminals for the control of the whole gate. Figure 11 shows a 24-bit register with transfer paths from another 24-bit register.

Fig. 11

There is no requirement that the interconnecting Data Cables for the register segments be of identical lengths To compensate for differences in length, the validity of the data from each source module is individually checked via its own Data Cable.

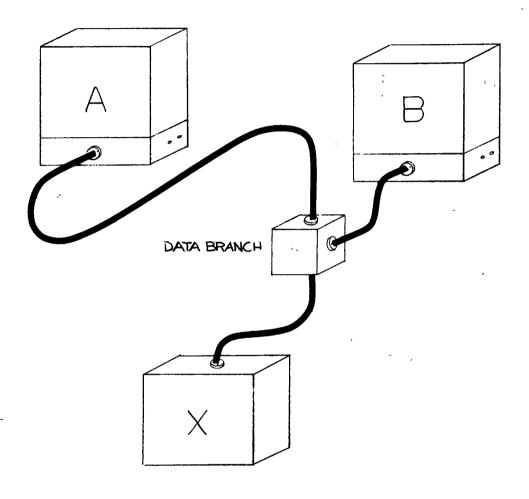

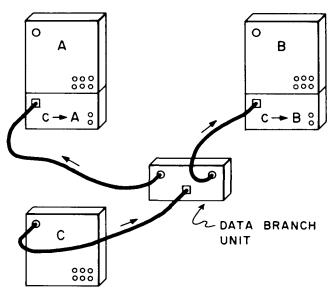

In order to permit the transfer of information from a single source into more than one destination module, a <u>Data Branch</u> unit is used (Fig. 12).

Fig. 12

Data Branch units may be interconnected (see Fig. 13) to provide any number of connections to the same source.

Fig. 13

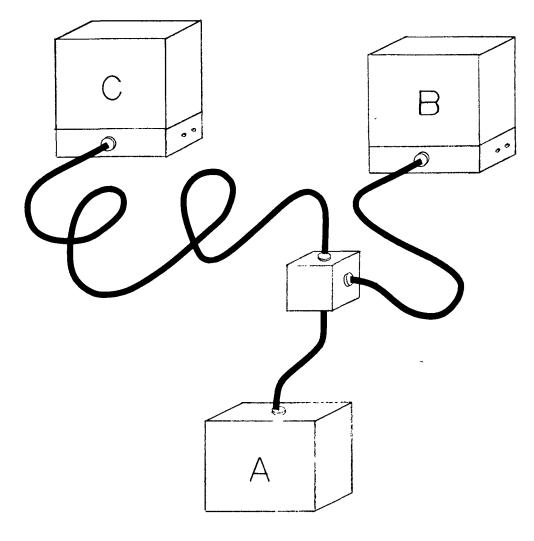

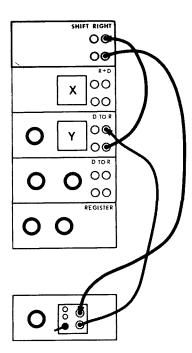

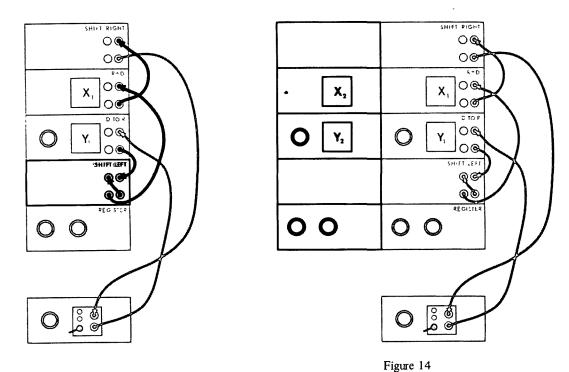

The Data Branch unit is only a way-station and not a source of data. Therefore, when it receives a Validation Request Signal, it relays it down-stream to the source. The unit remembers which branch carried the Validation Request Signal, and when the Validation Signal returns, it is relayed up that, and only that, branch. The importance of this feature is made clear in Fig. 14.

Fig. 14

Suppose that the sequence

- 1) A → B

- 2) COMPLEMENT A

- 3) A → C

is to be performed, and that Validation Signals are transmitted from the Data Branch unit toward both B and C. It would then be possible for the Validation Signal from step 1 to arrive at the  $A \rightarrow C$  Data Gate after the Validation Request Signal for step 3 had been sent but before the corresponding Validation Signal for step 3 returns. At that time, the original uncomplemented data from A would still be present at the Data Gate and would be transferred into C by the premature arrival of the Validation Signal from step 1, and an erroneous completion signal would be produced. Such incorrect behavior is prevented by arranging matters so that a Validation Signal is returned only to the element which issued the Validation Request Signal.

The Data Branch unit embodies all of the features essential to a Data Cable extender (i.e., data signal amplification, ability to relay data validation signals, etc.). This unit therefore doubles as an extender unit for Data Cables (Fig. 15).

Fig. 15

Finally, it must be pointed out that two registers cannot exchange information without the aid of a third register. This follows from the fact that simultaneity of events in different parts of an asynchronous system cannot be assumed.

### Memory

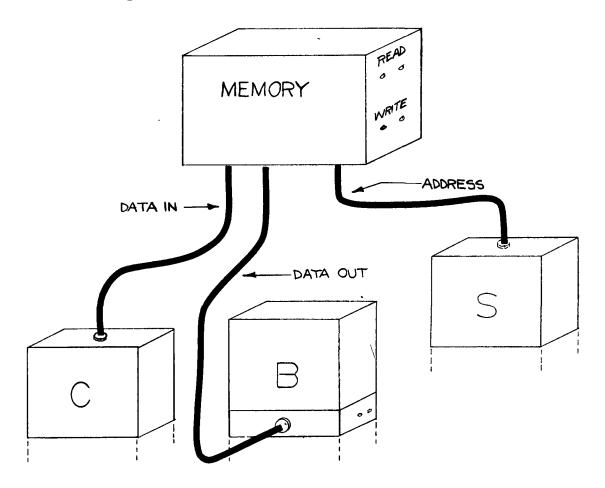

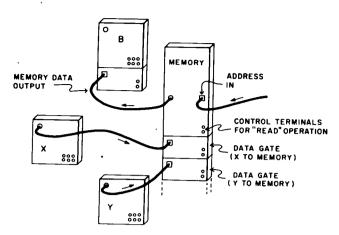

The Memory Module has a capacity of 4096 12-bit words and contains, in addition to a memory array, all required drivers, addressing logic, sense amplifiers, internal address and data registers, etc. The units may be plugged together, as discussed below, to form larger memory systems. (Intermodule connectors are omitted from the figures for simplicity.)

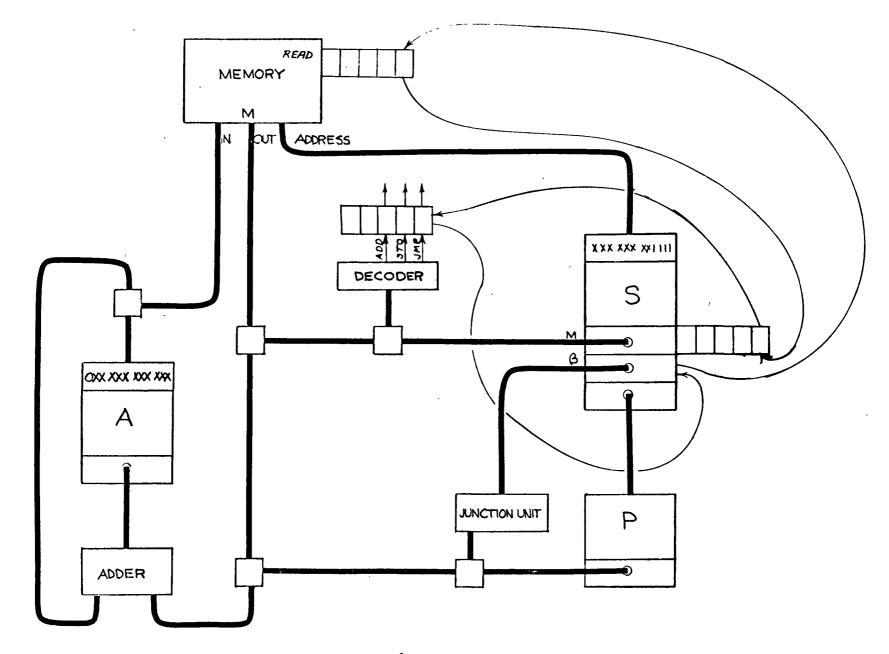

Figure 16 shows a simple arrangement in which one Memory Module is used. The unit marked S is a Register Module whose output is connected to the Address Input of the Memory Module, the unit marked C is a Register Module whose output is connected to the Data Input of the Memory Module, and a Data Gate attached to Register Module B is connected to the Data Output of the Memory Module. Initiation and completion terminals are provided for both Read and Write operations.

Fig. 16

The process of Reading involves two steps:

- Step 1. An address is transferred into the memory's internal address register.

- Step 2. The Read operation is performed and the word obtained is presented at the unit's Data Output terminals.

These two steps are initiated by a control signal on the Read operation's initiation terminal and proceed automatically to conclusion with a completion signal appearing as soon as step 1 is finished so that the system may execute other operations while waiting for step 2, typically a relatively long operation, to be completed. S may be changed any time following the completion signal without affecting the Read operation.

In this example the Memory Module Data Output terminals are connected so that the word obtained from the memory array may be transferred into B. The Read operation's completion signal or any subsequent signal may be used to initiate this transfer operation. If the Memory Module has not yet finished step 2, the Validation Signal to the Data Gate is held up until the word is available.

Writing a word into the memory involves the following set of operations:

- Step 1. An address is transferred into the memory's internal address register, and the word to be written is transferred into the memory's internal data register.

- Step 2. The Write operation is performed.

These operations are initiated when a control signal is presented at the Write operation's initiation terminal and, as in the case of the Read operation, a completion signal appears as soon as step 1 above is completed. Thereafter, registers C and S may be disturbed without affecting the Write operation.

If an attempt is made to read from or write into the memory while it is still responding to some earlier control signal, the new control signal will be held up until it can be accommodated.

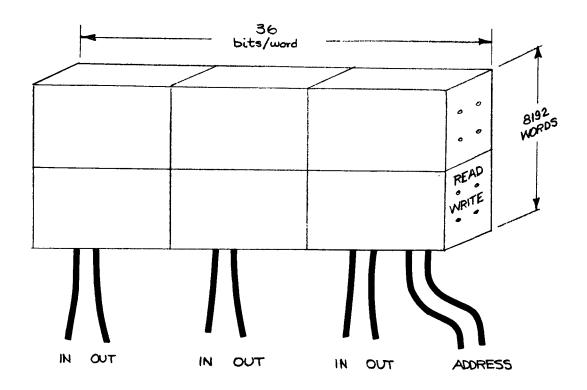

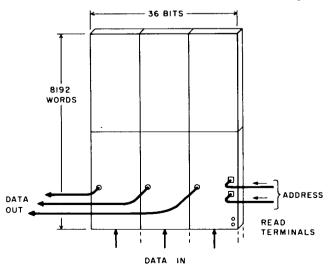

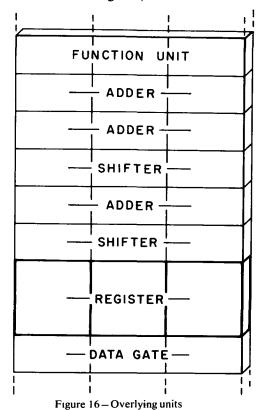

Memory Modules can be plugged together laterally to increase word length, thereby forming what will be referred to as tiers. These tiers may be stacked vertically to increase the number of words. Figure 17, for example, shows a memory system containing 8192 thirty-six bit words.

Fig. 17

To permit referencing in memory systems containing more than 4096 words, connectors are provided for additional Address Inputs for selection of the appropriate tier. All address information is provided to the lower rightmost unit which distributes this information throughout the assemblage for proper word selection. Similarly, the entire assemblage is controlled by signals at the Read and Write control terminals on the lower rightmost unit. For input and output data paths, each vertical column uses the data terminals on the lowest tier.

Concurrent operation of different memory tiers is possible. That is, during step 2 of a Read or Write operation in one tier, a Read or Write operation in another tier may be initiated and will proceed immediately. However, the data resulting from one Read operation must be used before another Read operation is initiated.

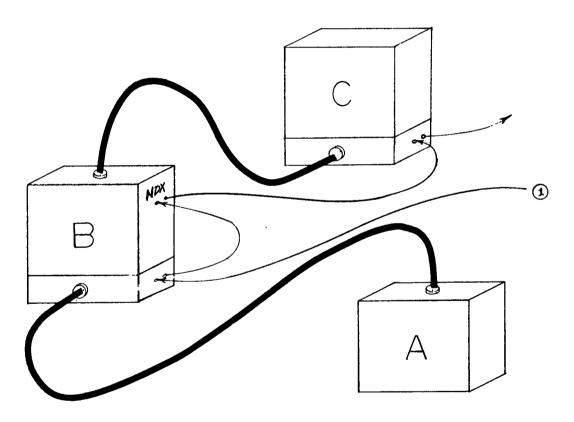

### Time-Continuous Transformations

Three units are provided which perform time-continuous transformations of data. These units continuously present at their outputs a transformation of the data presented at their inputs. When the input information changes, the outputs will reflect this change. These units thus perform their functions continuously in contrast to Register Modules and Data Gates, which react only to command signals presented at a discrete time.

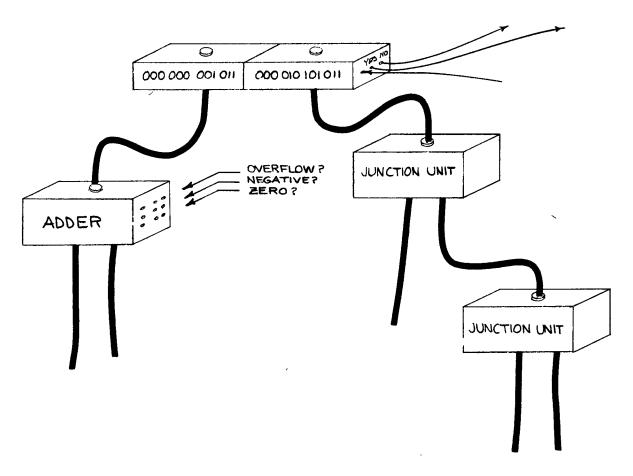

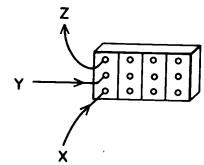

The Junction Unit, Adder Unit, and Function Unit discussed below all perform time-continuous transformations. The outputs of these units may be used in the same way in which Register Module outputs are used.

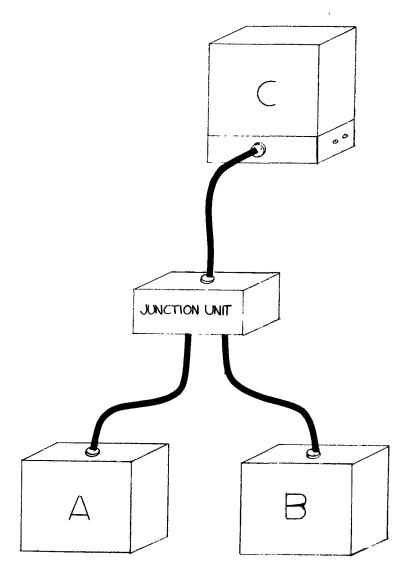

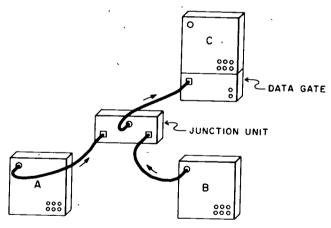

### Junction Unit

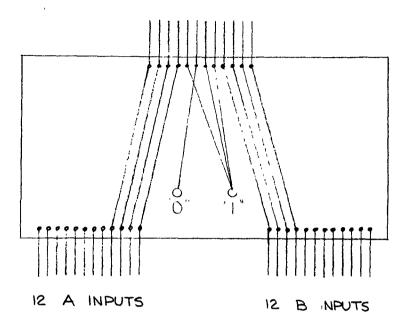

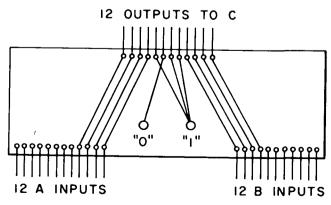

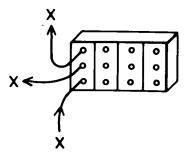

A Junction Unit permits one to rearrange bits within a word or to form words from bits selected from several words. The unit has two 12-bit data inputs and a single 12-bit data output. A set of switches on the face of the unit can be set to connect each of the 12 output terminals to any of the 24 input terminals or to supply the value "1" or "0".

Suppose, for example, that we wish to transfer information from parts of two 12-bit registers, A and B, into a third register, C. Specifically, suppose that we wish to copy the rightmost four bits of A into the leftmost four bit positions of C, the leftmost four bits of B into the rightmost four bit positions of C, and set the four middle bits of C to the binary value 1011. To accomplish this we connect the units as shown in Fig. 18, setting the switches on the Junction Unit to perform the transformation as shown in Fig. 19. The word made up by the Junction Unit is transferred into C via a Data Gate.

Fig. 18

### 12 OUTPUTS TO C

Fig. 19

Let us look briefly at the process of data validation in the preceding example. When the Data Gate is activated, it transmits a Validation Request Signal to the Junction Unit which in turn sends Validation Request Signals to each of the sources, A and B. When Validation Signals have returned to the Junction Unit from both sources, the Junction Unit transmits a Validation Signal back to the Data Gate.

For the permutation of bits within a 12-bit word, only one of the two inputs is used. The absence of a cable on the unused input connects the Validation Request Signal line to the Validation Signal line on that side, thereby indicating constant validity.

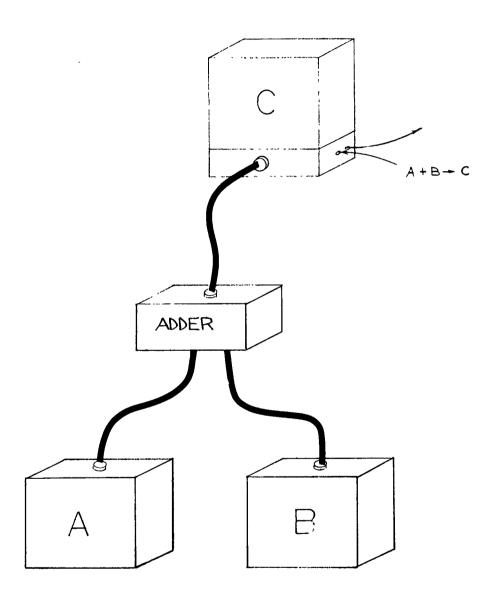

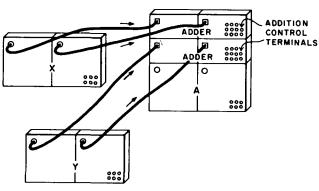

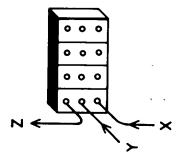

### Adder Unit .

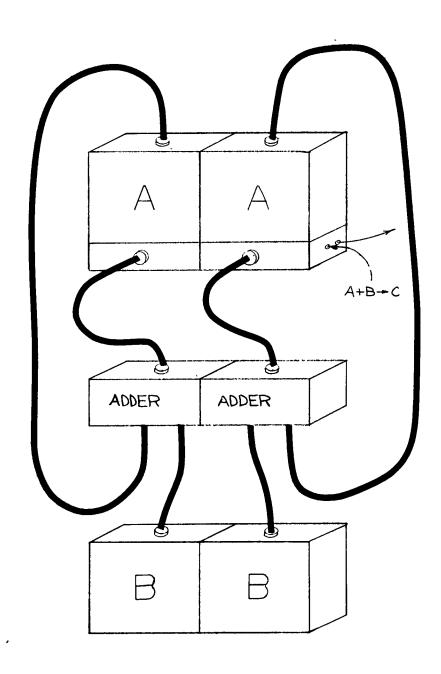

The basic Adder Unit is like the Junction Unit in general form. It receives inputs from two 12-bit sources and, from these, forms a sum which is continuously presented at its output terminals. Figure 20 shows an Adder connected to form the sum of the numbers in A and B. An initiation signal at the Data Gate transfers the sum into C.

Fig. 20

Adders for larger registers are formed by plugging Adder Units together laterally. Carries are propagated from unit to unit through connectors at their interface, which also interconnect internal circuits compensating for the increase in carry propagation time. Figure 21 shows a 24-bit accumulator, A, to which the contents of register B are added when a control signal is presented at the Data Gate.

Fig. 21

Before a sum is used at a destination module, a validity check is performed. When an Adder Unit receives a Validation Request Signal, it in turn sends Validation Request Signals to both input data sources. After both sources have returned Validation Signals and formation of the sum has been completed, the Adder Unit returns a Validation Signal to the destination.

The Adder Unit contains three decision nodes which provide for the detection of overflow, negativity, and the numerical sum zero. Their use is discussed below in the section dealing with control decisions.

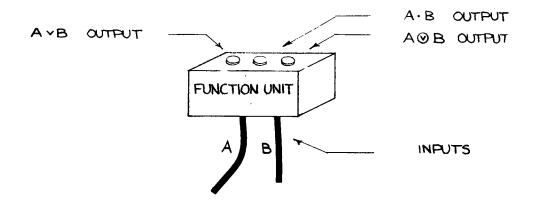

### Function Unit

A Function Unit (Fig. 22) performs three logical operations on a pair of data inputs. These operations are the logical "OR" ( $\mathbf{v}$ ), the logical "AND" ( $\mathbf{\bullet}$ ) and the "EXCLUSIVE OR" ( $\mathbf{\Theta}$ ). The results of these operations are presented at three 12-bit data output connectors.

Fig. 22

Data Validation in the Function Unit is similar to that in the Adder and Junction Units. However, as in the Data Branch unit, Validation Signals must be returned only to a destination from which a Validation Request Signal has been received.

## Sequencing

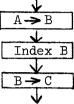

In order to perform a desired sequence of operations, control signals are routed along Control Cables from one set of control terminals to the next set in a manner reminiscent of the plugboard programmed machines or the Bell Computer Model VI. 3 Thus to perform the sequence

one would interconnect control terminals as follows.

Fig. 23

When a signal on line labeled (1) arrives at the control terminal on the  $A \longrightarrow B$  Data Gate, it initiates the transfer of data from A into B. The completion signal from this operation is routed to the control terminal which indexes B, and its completion signal is, in turn, routed to the initiation terminal on the  $B \longrightarrow C$  Data Gate, etc.

## Concurrent Sequences

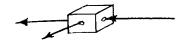

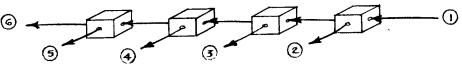

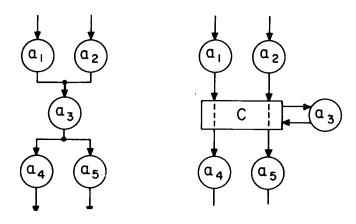

Use of the <u>Control Branch</u> unit makes it possible to perform sequences of steps which may be executed concurrently. A control signal presented at the input terminal of such a unit causes control signals to appear on each of two output terminals (Fig. 24).

Fig. 24

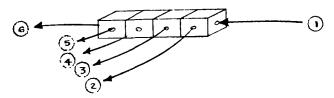

The Control Branch unit contains amplifiers associated with each output sufficient to drive the maximum standard length of Control Cable, and therefore is may also be used to <u>extend</u> Control Cables. These units may be interconnected to form an arbitrary number of control path branches (Fig. 25).

Fig. 25

A signal on line 1 will cause signals to appear on lines 2 through 6. Alternatively, the units may be plugged directly together (Fig. 26).

Fig. 26

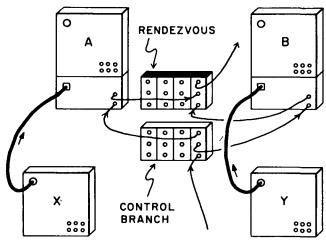

In general, in the operation of two concurrent sequences, there will be found a point at which ensuing steps can be taken only after all steps of both sequences have been completed up to that point. A Rendezvous Unit (Fig. 27), which produces a signal at its output terminal only after signals have arrived at both of its input terminals, is used at the point of conjunction. (A Rendezvous Unit can thus be identified as a Muller C-unit 1.)

Fig. 27

<sup>\*</sup> The Rendezvous Unit is shown with a darkened top to distinguish it from units of a similar appearance.

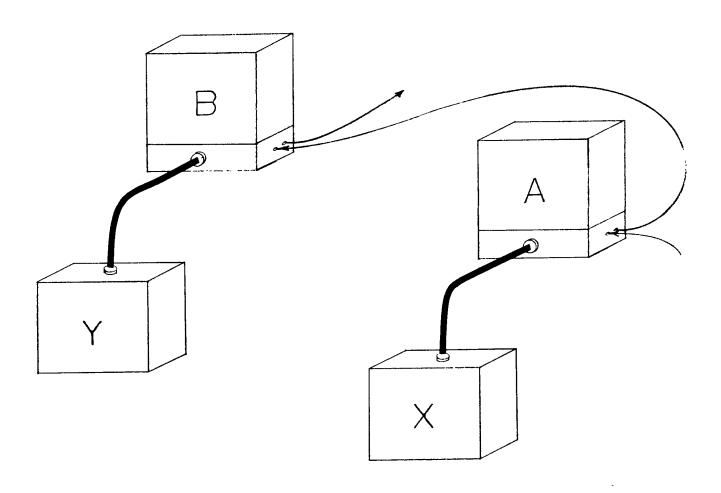

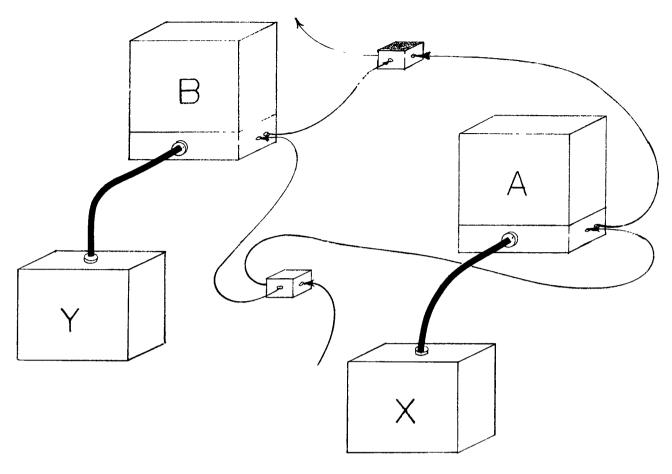

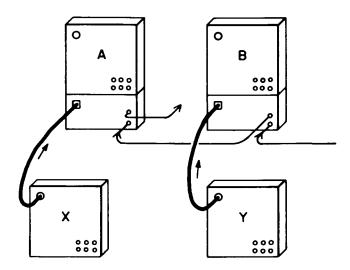

For example, suppose that we have a problem which requires several set-up steps, one of which transfers data from register X to register A, and another of which transfers data from register Y to register B. These steps may either be executed sequentially (Fig. 28), or they may be executed concurrently (Fig. 29).

Fig. 28

Fig. 29

In the latter case, both transfers are activated and can take place at more or less the same time. As each transfer is completed, a signal is sent to the Rendezvous Unit. When both signals have arrived, the unit sends out a signal which proceeds on to the next step.

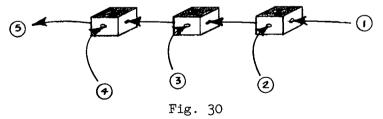

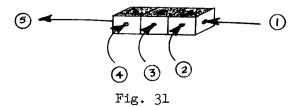

A signal indicating the completion of an arbitrary number of concurrent actions can be generated as shown in Fig. 30.

This signal will appear on line 5 only after signals have been received on lines 1 through 4. The same end may be achieved by plugging the units together as shown in Fig. 31.

## Call Unit

For those situations in which more than one control path must have access to a single pair of control terminals, calling elements must be used. Five such calling elements are included in a single Call Unit.

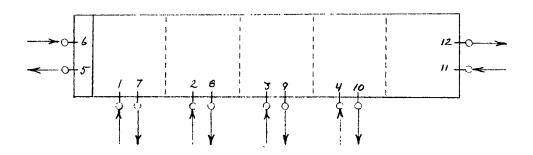

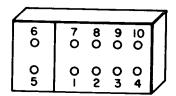

A Call Unit is provided with the following terminals:

Fig. 32

1, 2, 3, 4 and 11 are input terminals for the elements; 7, 8, 9, 10 and 12 are the output terminals. Terminals of the fifth element are positioned at the right end of the unit to permit easy extension, as discussed below. Dotted lines show the separations between the elements. Whenever a control signal arrives at the input terminal of one of the calling elements, a control signal is presented at terminal 5. When the unit is plugged onto a pair of operation control terminals, terminals 5 and 6 mate with the operation's initiation and completion terminals respectively. The signal produced at terminal 5 thus initiates the operation. When the completion signal from this operation is presented at terminal 6, the Call Unit, in turn, produces a completion signal at the output terminal of the element which called for the operation.

Figure 33 shows a Call Unit attached to the <u>Complement</u> control terminals of a Register Module.

Fig. 33

When Call Units are plugged together (Fig. 34), terminals 5 and 6 of the right hand unit mate with terminals 11 and 12 of the left hand unit. The unit on the right calls its left neighbor via that unit's fifth calling element, the completion signal returning to the right hand unit through the junction of terminals 12 and 6.

Fig. 34

Figure 35 shows a Register Module with two Call Units on the  $\underline{\text{Index}}$  operation terminals.

Fig. 35

Note that the control path shown calls for the execution of two  $\underline{\underline{\text{Index A}}}$  operations in sequence.

Call Units may be attached to the control terminals for any operation. Figure 36 shows three control paths, two of which contain a step which transfers A to B, and two of which index A.

Fig. 36

The three sequences performed are:

| (1)<br>COMPLEMENT A           | (2)               | (3)<br>INDEX A |

|-------------------------------|-------------------|----------------|

| $\underline{A \rightarrow B}$ | <u>A</u> → B      |                |

| COMPLEMENT B                  | $B \rightarrow C$ |                |

No Call Units are required on the complement A, complement B, and  $B \to C$  operation terminals, as each of these operations occurs in only one of the above sequences.

A Call Unit need not be plugged directly onto a pair of operation control terminals. It may, instead, be connected by means of control cables (Fig. 37).

Fig. 37

Similarly, extension may be accomplished with cables (Fig. 38).

Fig. 38

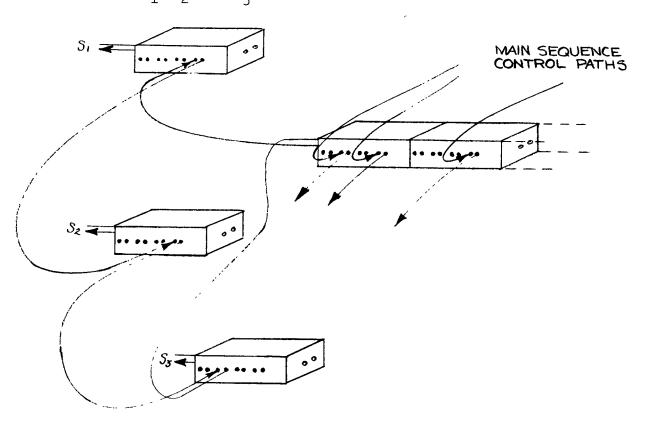

## Sub-Sequence Calling

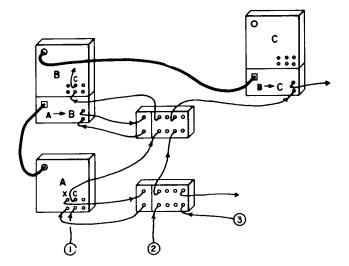

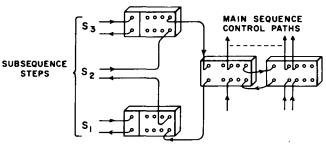

Suppose, now, that several main sequences have a common subsequence (for example, an <u>operand fetch</u> sub-sequence common to several instructions). After completion of the steps of the sub-sequence, each main sequence must continue with its own set of steps (corresponding perhaps to different instruction execution steps).

Figure 39 shows the Call Units which are associated with the steps of the sub-sequence and, without showing the steps explicitly, merely indicates them as  $S_1$ ,  $S_2$ , and  $S_3$ .

Fig. 39

All of the instructions signal the Call Unit assemblage on the right at the point at which they require an operand. This stack calls on a series of other Call Units, each of which in turn performs a step of the Operand Fetch sub-sequence. After all steps are completed, a signal is returned to the main calling assemblage, from which each instruction's control signal proceeds to initiate succeeding steps defining that particular instruction. Essentially, then, a Call Unit remembers which main control path is calling for the performance of a step or a set of steps during the execution of those steps.

### Control Decisions

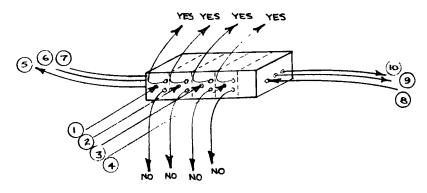

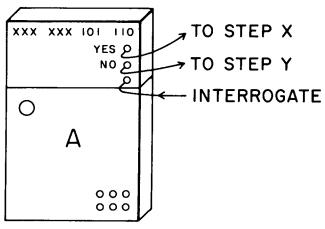

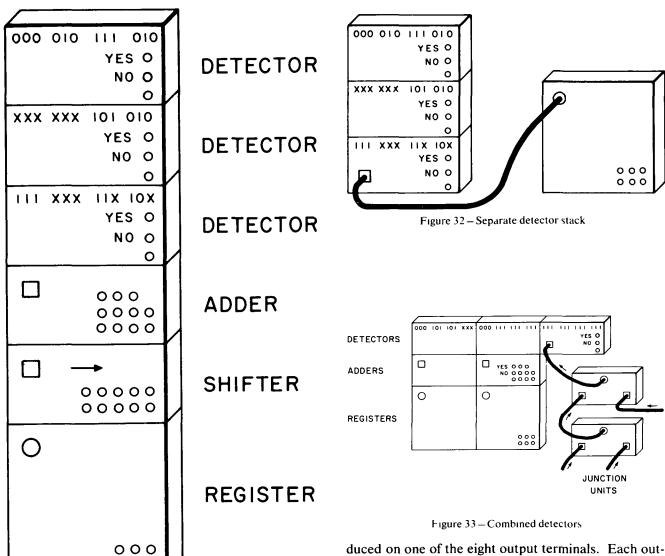

In order to permit the choice of alternative steps to be made on the basis of data held by the system, two Processing Network elements, a Detector Unit and a Decoder Unit, are provided.

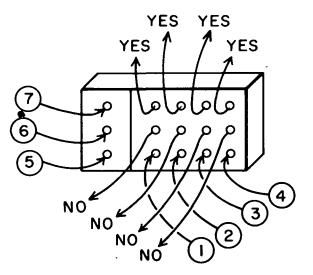

A <u>Detector Unit</u> is used to detect a specific value on a data path. It may be plugged directly onto the unit which provides the data or it may be connected via a Data Cable to a source of data. A data input connector on its base is provided for this purpose.

The binary value to be detected is entered in a set of 12 switches on the unit. A third setting of each switch allows one to indicate indifference to the value of the bit in that position.

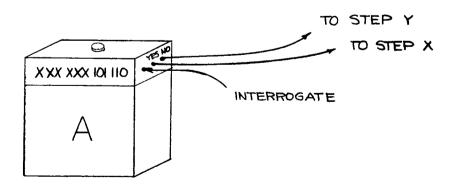

A Detector Unit has three control terminals, one for interrogation and the others to indicate the result. When a control signal interrogates the Detector Unit, a data validity check is first performed and the data is then compared with the pattern set in the switches. If the pattern matches the data, a control signal will be presented at the "Yes" terminal. If the pattern does not match the data, a control signal will be presented at the "No" terminal.

For example, suppose that whenever register A contains the binary number 101110 in its rightmost 6-bit positions it is desired to perform some step X, whereas, otherwise, step Y is to be performed. A Detector Unit must be set to detect the desired pattern. The leftmost six switches are set to indicate indifference. The remaining switches are set to read 101110. The Detector Unit is then connected to Register Module A, and the control terminals are connected as shown in Figure 40.

Fig. 40

The Detector Unit, in addition to the above function, passes the data from its input connector through the unit to a data output connector on its top surface, thereby making the register output information available for other possible uses.

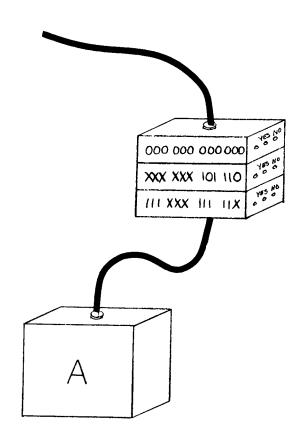

Detector Units can thus be stacked, making it convenient to test for any of a variety of possible patterns of interest. Figure 41 shows three Detector Units connected to a single Register Module. They are stacked on top of one another, but in this case they are shown at a distance from the source register and hence are connected to it by a Data Cable. The cable extending above the Detector Unit stack carries the data from A on to other modules.

Fig. 41

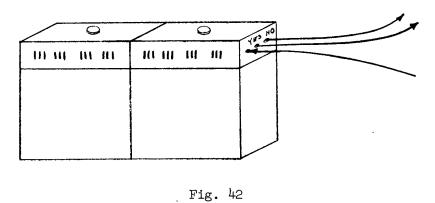

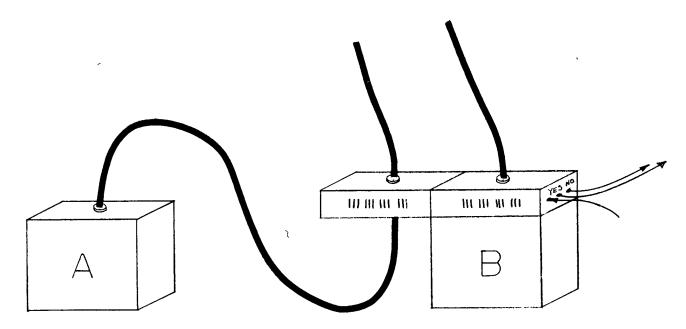

Detector Units can be plugged together laterally for the detection of patterns of more than 12 bits (Fig. 42). The set of control terminals on the rightmost unit serves for the entire assemblage. No detection decision is made until the data from all sources has been validated.

Figure 43 shows an arrangement which detects a pattern of 24 bits contained in two separate 12-bit registers, A and B.

Fig. 43

Figure 44 shows an arrangement which detects a pattern of 24 bits from a variety of sources.

Fig. 44

The Adder Unit, as mentioned earlier, has three sets of detector terminals. These terminals are similar to the control terminals on the Detector Unit and are used in an equivalent manner for detection of carry overflow, negativity, and the numerical sum zero. A signal returned at a "Yes" terminal indicates that the associated condition exists.

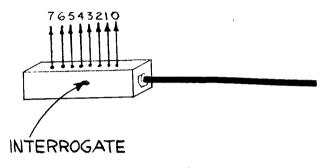

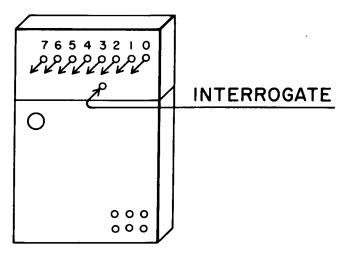

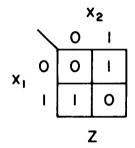

Detector Units make it possible to select one of two alternative control paths on the basis of particular data values or patterns. Sometimes, however, it is desirable to select one of 2<sup>n</sup> paths on the basis of n bits of data. In this case 2<sup>n</sup> detectors might be used, but the number of detectors required grows rapidly with n. Instead, therefore, a <u>Decoder Unit</u> is provided (Fig. 45). This unit contains a 3-bit decoder which may be interrogated by a control signal.

Fig. 45

The cable shown entering the side of the unit is a standard Data Cable coming from some source. The input data is passed through the detector to a data output connector on the opposite surface of the unit. On the face of the Decoder Unit, switches are provided for selecting three of the 12 data lines for decoding. When a control signal arrives at the interrogate terminal (also on the front face of the unit), the data is validated and then a signal is produced on one of the eight output terminals (shown on top). Each output terminal corresponds to one of the eight possible values encoded on the selected bits, and the signal appears at the corresponding terminal.

To permit decoding of values encoded on fewer bits, the switches for bit selection include a position which supplies an apparent "0" to the decoder. If, for example, the most significant bit of the decoded subset is thus fixed, an output signal will never appear on lines 4, 5, 6, or 7.

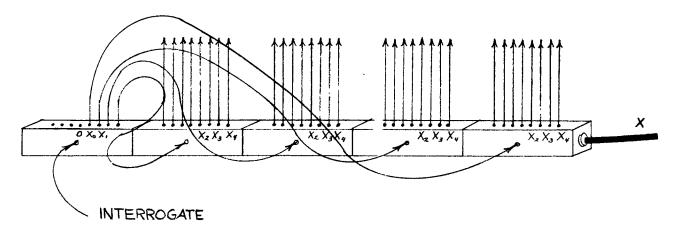

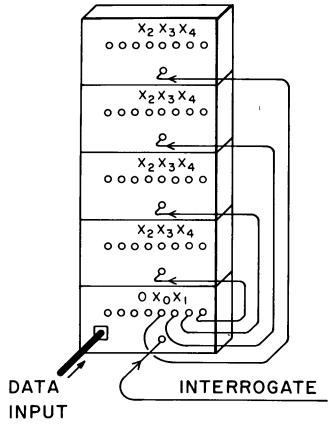

To illustrate the technique of decoding values encoded on a larger number of bits, let us consider the problem of selecting one of 32 alternative control paths. To be explicit, let us label the 12 data lines  $X_0$ ,  $X_1$ , . . .  $X_{11}$  and let us suppose that we wish to decode the value on lines  $X_0$  -  $X_1$ . Figure 46 shows the necessary connections.

Fig. 46

Note, first of all, that the Detector Units can be plugged together laterally. This passes the data on the X data cable to all of the units. Each unit is labeled to indicate which lines are selected for decoding. The leftmost unit decodes the value on two lines,  $X_0$  and  $X_1$ . When the interrogate signal arrives at the leftmost unit, a signal will appear on one of four output lines as shown, depending on the states of  $X_0$  and  $X_1$ . This signal is routed to the interrogate terminal of one of the other Decoder Units which, based on the values on  $X_2$ ,  $X_3$ , and  $X_4$ , in turn produces a signal on one of its eight output lines. Extensions of this technique make it possible to decode data values encoded on any number of bits.

## Merge Unit

At some point after making a decision, all of the decision-dependent steps will have been executed, and the corresponding alternate control paths may be joined through the use of a Merge Unit.\* This unit produces a signal at its output terminal whenever a signal appears at either input terminal (Fig. 47).

Fig. 47

Figure 48 shows these units connected to merge four control paths. An input signal on any of lines 1, 2, 3, or 4 will produce an output signal on line 5. The units may also be plugged directly together laterally as shown in Fig. 49.

Fig. 48

Fig. 49

<sup>\*</sup> This unit, like the Control Branch, may be used to interconnect and thereby extend Control Cables.

## Decision Call Unit

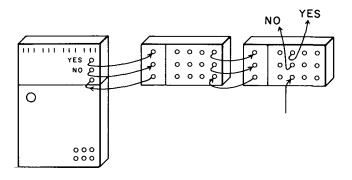

A <u>Decision Call Unit</u> permits a detector unit to be accessed by more than one control path and contains five decision calling elements as shown in Fig. 50.

Fig. 50

This unit plugs directly onto the control terminals of a Detector Unit, terminal 5 mating with the interrogate terminal and terminals 6 and 7 with the "Yes" and "No" terminals as shown below.

Fig. 51

When a control signal is presented at the input of any of the five decision calling elements, a signal is produced at terminal 5 which interrogates the Detector Unit. A "Yes" or "No" signal is returned to the Decision Call Unit and will appear at the "Yes" or "No" terminal of the element which called for the interrogation.

Decision Call Units can be plugged together to allow an arbitrarily large number of control paths to access the same Detector Unit. Decision Call Units may also be connected to the Detector Unit by means of control cables as shown in Fig. 52.

Fig. 52

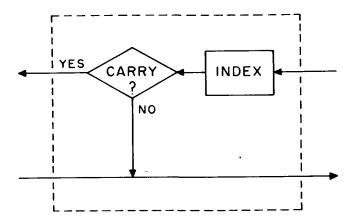

Like the Call Unit, the Decision Call Unit may be used to provide multiple access to a sub-sequence control path. In this case, the subsequence may include a decision in which one of two alternative control paths is selected. In this context the Decision Call Unit may be thought of as calling a subroutine which has two return points. A simple example of this is shown in Fig. 53. Register C is used as a counter which, whenever indexed, is checked for the value 77778. The use of the Decision Call Unit allows this counter to be used by many different control paths. Obviously any number of steps may occur in the sub-sequence prior to or following the decision.

Fig. 53

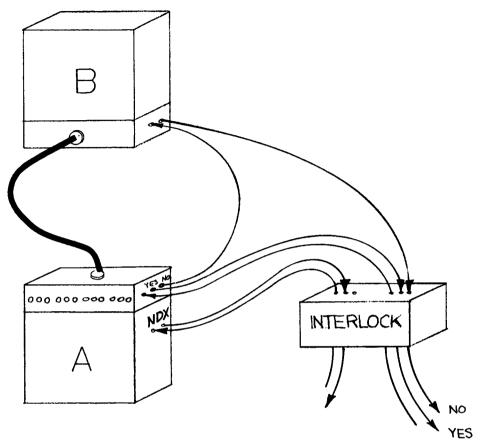

### Interlocking

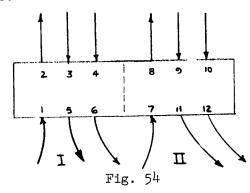

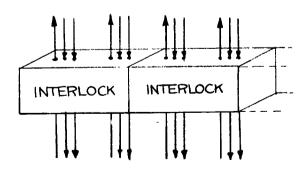

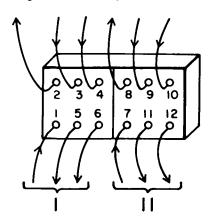

In some situations two independent sequences will both require the use of the same data-processing element(s), (e.g., two sequences which make use of the same memory), and conflicts may arise. For such situations an Interlock Unit (Fig. 54) is provided. This unit sorts incoming control signals on a "first-come, first-served" basis, interlocking them in such a way as to resolve conflicts.

The left and right halves are associated with the control paths, I and II, of two concurrent sequences which must be interlocked. For a sequence to enter an interlocked phase, a signal must be presented to the interlock at an input terminal (terminal 1 for I, terminal 7 for II). Because it must be assumed that the sequences do not necessarily contain the same steps within their interlocked phases, each control path is provided with its own terminals (terminals 2, 3, 4 for I; terminals 8, 9, 10 for II) for use during the interlocked phase. If the interlock is off when a signal arrives at terminal 1, it is turned on and a signal is produced at terminal 2. This signal is used to initiate the steps within the interlocked phase of the sequence associated with control path I. After the last of these steps has been completed, a signal is returned to terminal 3 or terminal 4. (Two return terminals are provided to allow for a possible decision within the interlocked section. If no such decision is required, either terminal 3 or 4 may be used for the return.) In either case, the return produces a signal at either terminal 5 or 6, depending on whether the return came to terminal 3 or 4, and shuts off the interlock. An equivalent process takes place for control path II, using terminals 7 through 12. If either control signal enters the interlock while it is on, it will be held up until the interlock is turned off. If signals arrive at terminals 1 and 7 simultaneously, only one will be accommodated immediately; the other will wait its turn.

Figure 55 shows an arrangement for interlocking two sequences, both of which use register A.

Fig. 55

Interlock Units can be plugged together (Fig. 56) to permit interlocking of any number of sequences.

Fig. 56

# EXAMPLES

Two examples of macromodular structures are now presented. The first is a simple multiplier. The second is a "central processor" for a small computer.

## Example No. 1 - A Multiplier

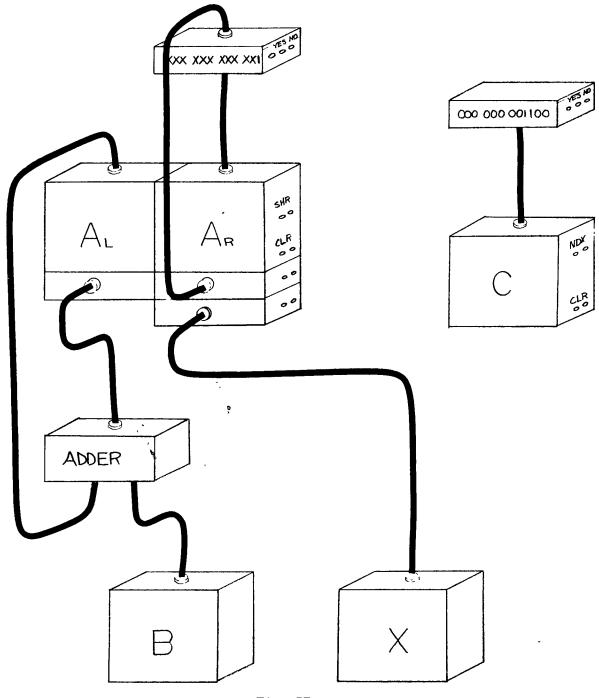

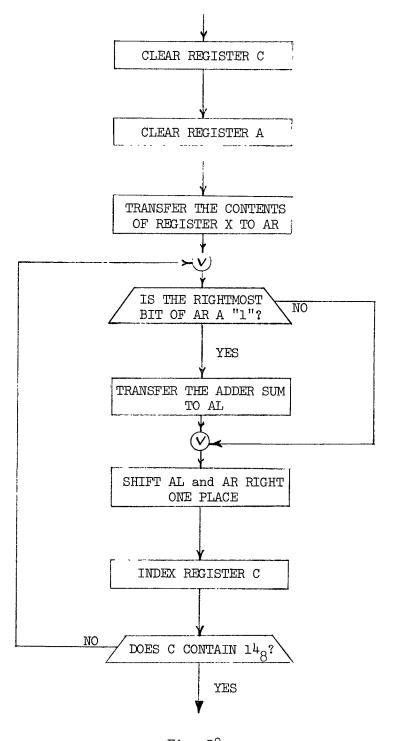

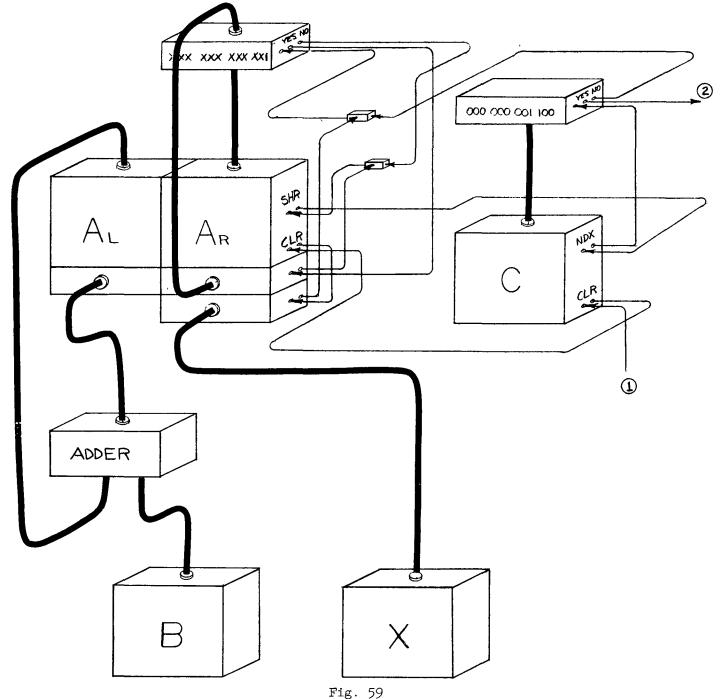

In this example, we will consider the multiplication of numbers with a positive sign and eleven bits of magnitude. The multiplier and the multiplicand are held in registers B and X, respectively, and the product is to appear in register A. Figure 57 shows the processing structure required.

Fig. 57

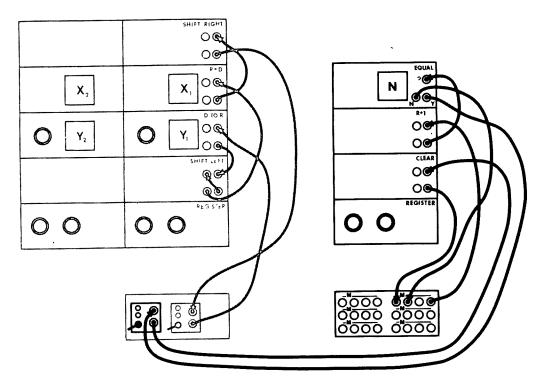

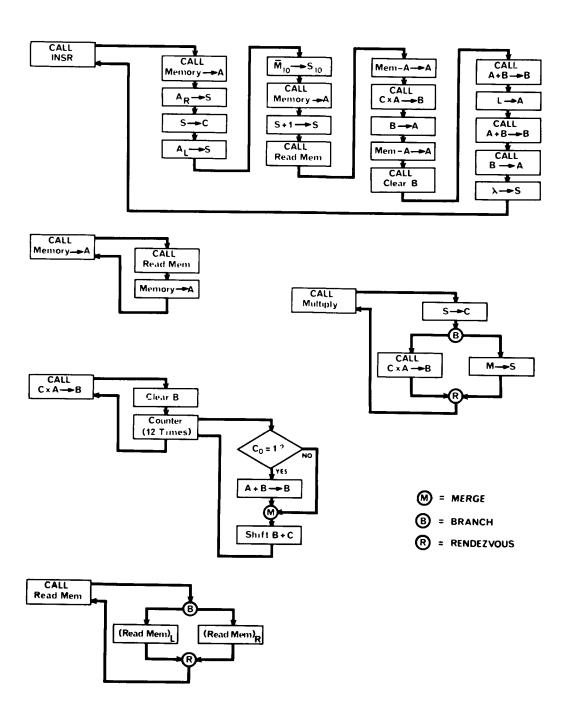

Figure 58 shows the algorithm to be used<sup>5</sup>. This algorithm calls for a succession of shifts and conditional additions while register C counts the number of times these steps are repeated. The process terminates when twelve  $(14_8)$  cycles have been completed.

Fig. 58

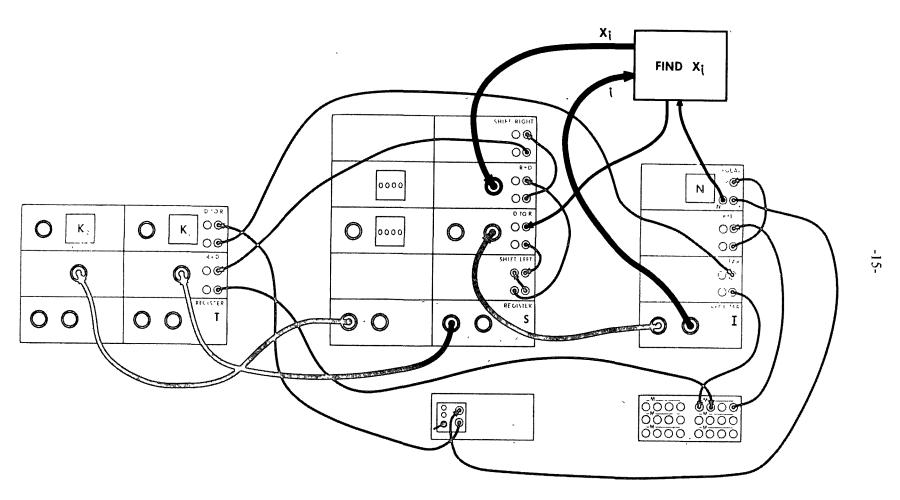

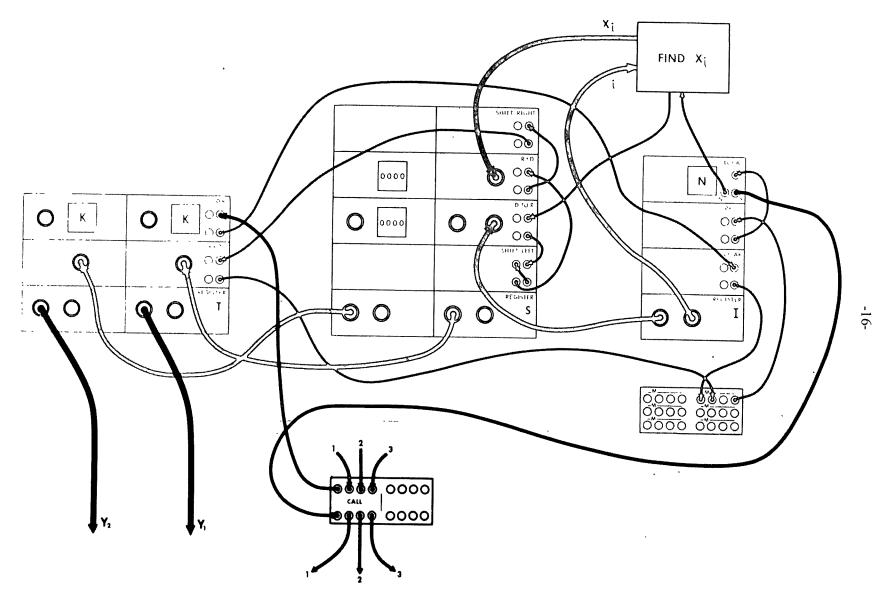

Figure 59 shows the addition of the sequencing network which controls the processing structure in such a way as to perform the multiplication according to the algorithm. The multiplication is performed whenever a signal is presented on line 1. A signal on line 2 marks the completion of the multiplication. Careful inspection reveals that the control lines shown have a one-to-one correspondence with the arrows which appear on the flow diagram. At the terminus of each control line, one of the functions described in the flow diagram boxes is performed.

## Example No. 2 - A Small Computer

Let us consider the central processing portion of a very simple computer and sketch out how it might be realized in macromodular form. The computer will have a 12-bit word length, 4096 words of programmable memory, and an instruction repertoire consisting of eight instructions encoded on the leftmost three bits of the 12-bit instruction word.

Three of the instructions make reference to other memory locations by a process of indirect addressing. These instructions are ADD  $\beta$ , STO  $\beta$ , and JMP  $\beta$  and use the contents of memory register  $\beta$  (0  $\leq$   $\beta$   $\leq$  777 $_{8}$ ) as the effective address. Thus, for example, if register  $\beta$  contains the number 1476, execution of an ADD  $\beta$  instruction will cause the contents of register 1476 to be added to the contents of the accumulator (in ones' complement form). Similarly, a STO  $\beta$  will store the contents of the accumulator in register 1476. A JMP  $\beta$  will cause the next instruction to be taken from location 1476.

The remaining five instructions do not make reference to other memory locations. Instead, they perform the following functions:

CLR - Clear the accumulator.

COM - Complement the contents of the accumulator.

APO - Skip the next instruction if the accumulator contains a positive number.

SHL n - Shift the contents of the accumulator n places to the left where n is specified by the four rightmost bits of the instruction word.

NOP - Proceed immediately to the next instruction.

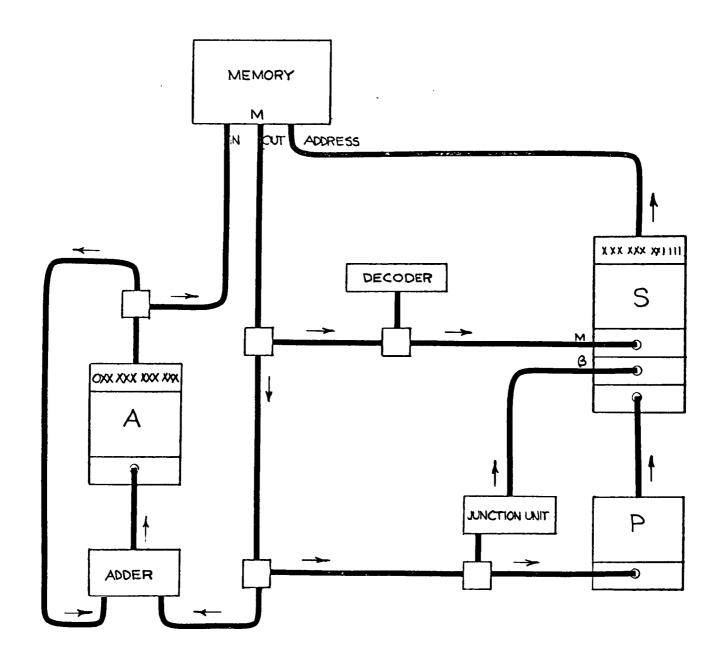

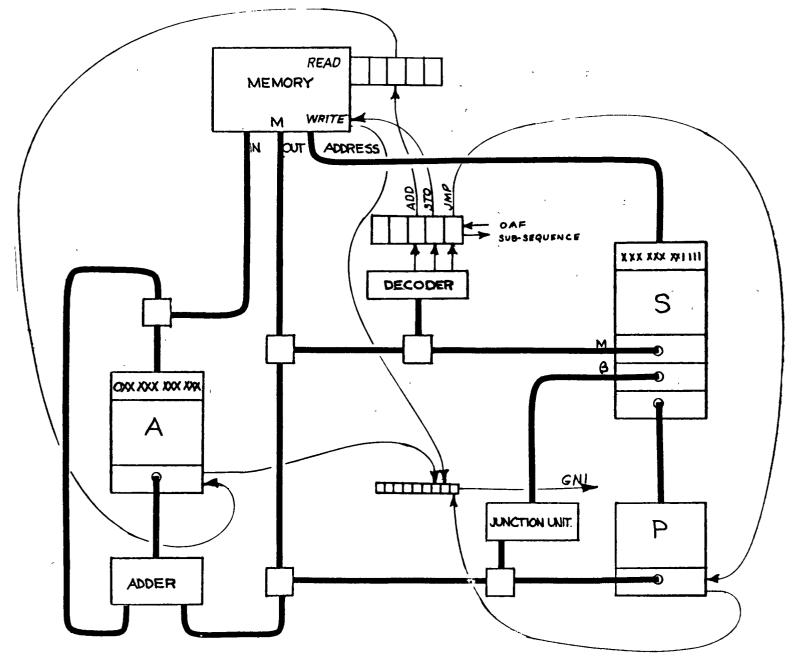

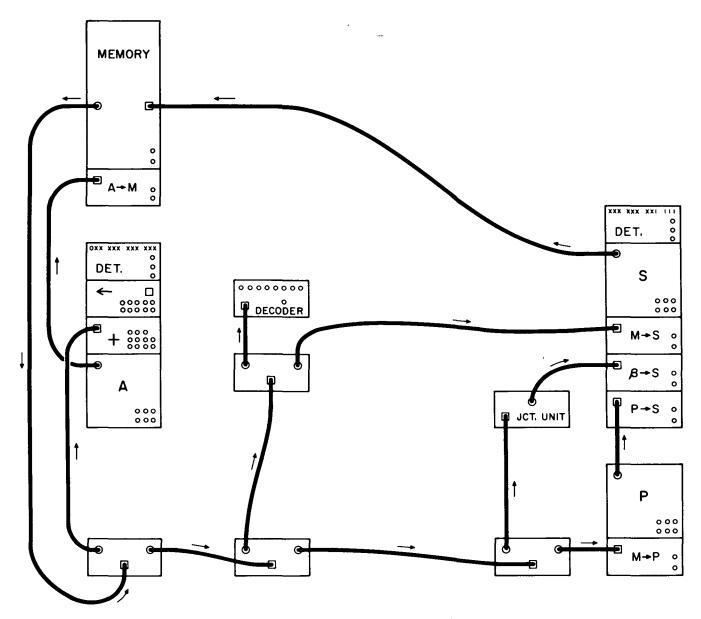

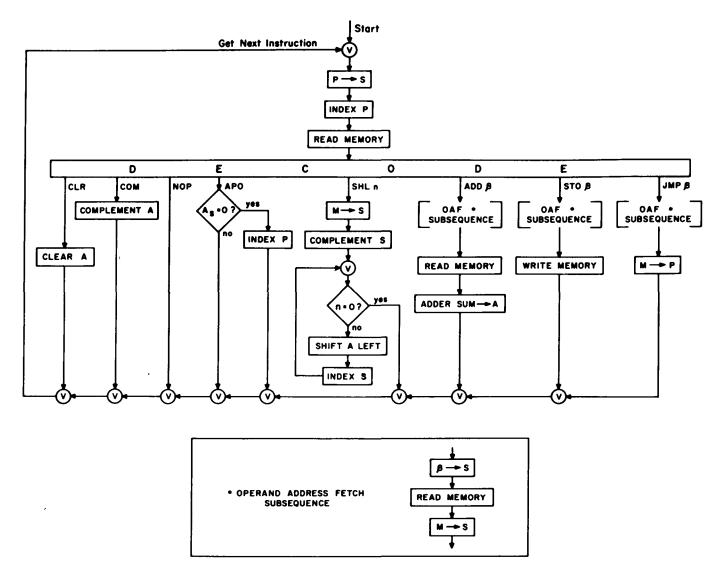

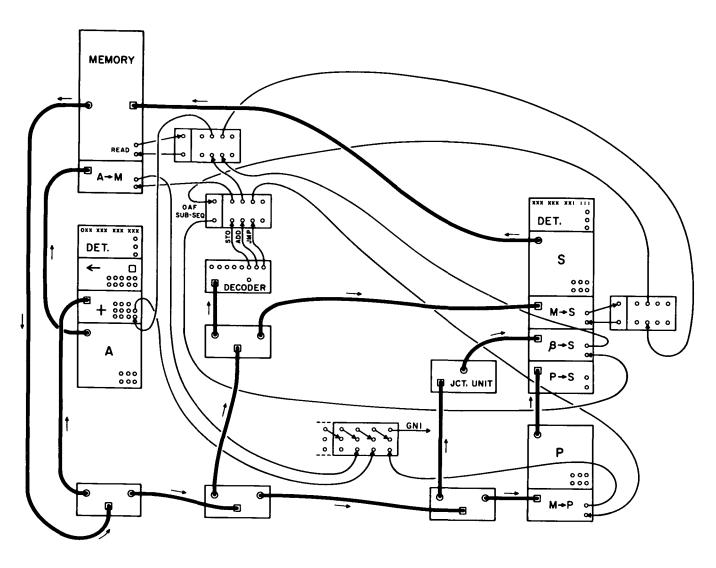

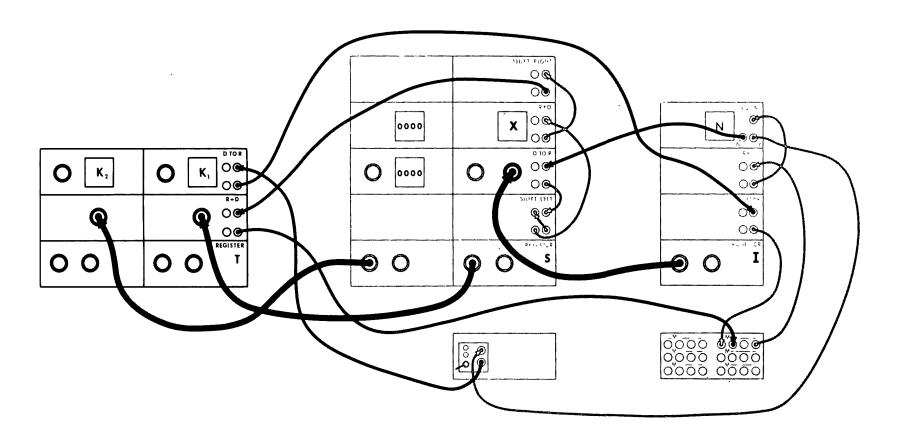

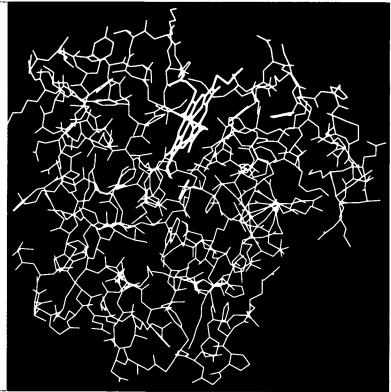

Figure 60 gives a two dimensional view of the processing network for this machine. Register A is the accumulator; register S is used to provide addresses to the memory and also to count out the number of shifts required by an SHL n instruction. During the execution of an instruction, register P holds the address of the next instruction to be executed. The Decoder Unit is set to decode the instruction field (3 most significant bits) of the word from memory, (M). The Junction Unit is set to mask out the instruction field when transferring 3 to S.

55

Fig. 60

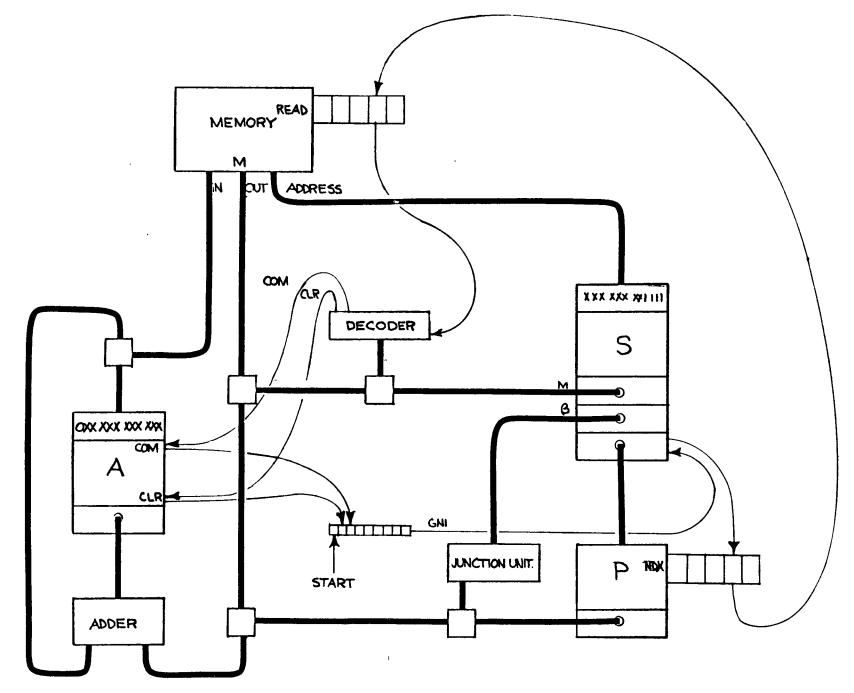

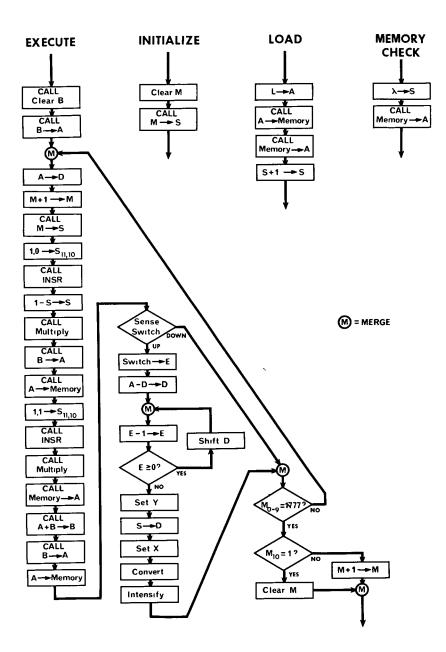

Figure 61 shows a flow diagram representation of the operation of the machine. Entering the top of the flow diagram corresponds to getting the next instruction from the memory. The contents of P are transferred to S in order to locate the instruction, and P is then indexed in preparation for locating the following instruction. Memory is read to obtain the instruction and the decoder is signaled to decode the instruction field of the memory word. Eight decoder output control paths are provided, one for each of the instructions, and a control signal is produced on the selected path. After the required sequence of steps has been executed, the control signal returns to get the next instruction, (GNI).

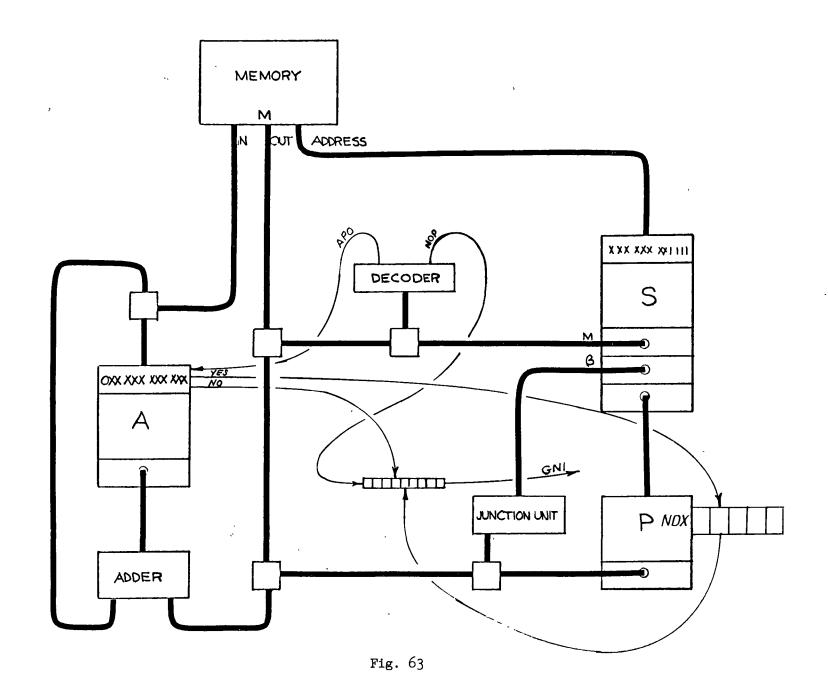

Figure 62 shows the control paths required to locate and decode the instructions, as well as the execution control paths for the instructions CLR and COM. Figure 63 shows the execution control paths for the instructions APO and NOP. The detector in the APO control path is set to detect a "O" in the leftmost (sign) position of the accumulator. A "No" signal response from the detector proceeds to the Merge Unit assemblage from which a signal to get the next instruction emerges. A "Yes" response indexes register P and then proceeds to get the next instruction. The NOP instruction has no execution steps, and its control path is routed directly to the GNI merge unit assembly.

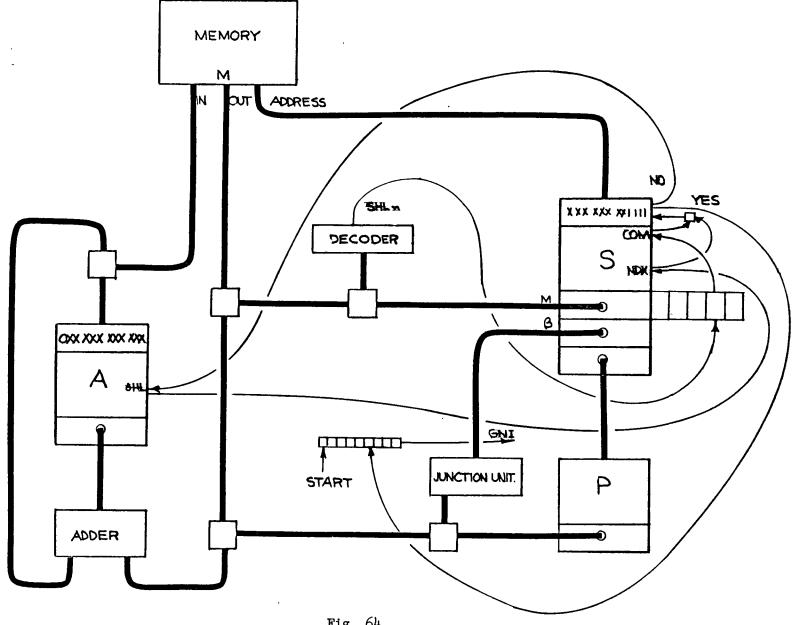

The SHL n instruction, shown in Fig. 64, uses the S register to count the number of places which have been shifted. The SHL n instruction word is transferred from the memory into S and complemented. A detector on S monitors the rightmost four bits, (n), and provides a "Yes" response when the value 178 (the minus zero in ones' complement form) is detected. A control loop is entered in which the detector is interrogated. A "No" signal response from the detector shifts A one place, indexes the count in S, and again checks the detector. This process repeats as long as more shifts are required. When the required number of shifts has been completed, interrogation of the detector will produce a signal at its "Yes" output, which is routed to the GNI Merge Unit assemblage.

The control paths for the three memory reference instructions are routed to a sub-sequence Call Unit. This sub-sequence fetches the operand address and places it in the S register. This three-step sub-sequence is shown separately on the flow diagram in Fig. 61, and the control path which realizes it is shown on Fig. 65. The first step of the sub-sequence is the transfer of to S. In the following steps, the effective address is obtained from

Fig. 62

Fig. 64

Fig. 65

Fig. 66

memory register  $\beta$  and transferred into S. Beyond this point the three instructions' control paths diverge, as shown on Fig. 66.

In the ADD instruction the memory is again read to obtain the operand. The adder forms the sum of this operand and the number in the accumulator, and in the next step of the sequence, the sum is transferred into A.

The STO instruction execution sequence consists simply of a single Write command to the memory, as Register A is connected directly to the memory Data Input.

In the JMP instruction, the effective address is transferred into P from the memory. For this instruction the final step of the operand address fetch subsequence (which put the operand address into S) was unnecessary but harmless.

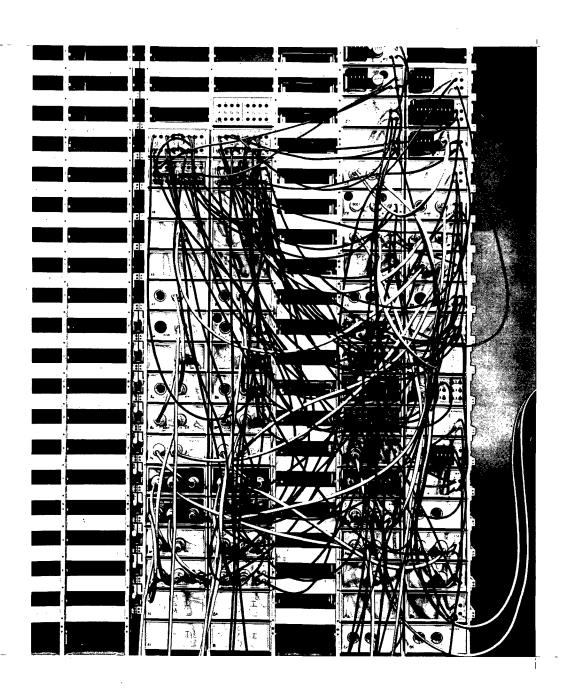

This example demonstrates the ease and directness with which simple systems may be put together. A total of 16 Data Cables, 35 Control Cables, and 17 modules or module assemblages are required to form this complete, albeit comparatively modest, central processor.

#### CONCLUSION

We have presented an approach in which flexibility and simplicity are brought to the forefront of factors relevant in computer design. Two aspects of this approach can be distinguished.

First, it adds an experimental element to the theoretical and simulational techniques now available to the system designer. Perhaps this can most effectively be employed in research groups having as their main objectives the creation of advanced computer systems for particular areas of work. Because of the relative ease with which a given configuration of macromodules can be profoundly altered, it is possible for such a group to work actively with several widely different forms in an attempt to find optimal configurations for different problem classes.

Second, it makes possible a smoothness of growth and refinement in an operating computing system. Because of the electronic independence of the macromodules, it is relatively easy to expand a macromodular system and to add new functions without seriously affecting the continuity of on-going work and without jeopardizing any existing investment in programs and operating procedures.

These properties of macromodular systems are of growing importance as we turn increasingly toward the user for new concepts in the search for more effective information processing systems.

### ACKNOWLEDGMENT

The authors wish to express their gratitude to J. R. Cox, Y. H. Chuang, T. J. Chaney, C. E. Molnar, and R. A. Ellis for their help in the development of the ideas presented here. Special thanks are due N. T. Kinch, R. E. Olson, and H. C. Lewis for the preparation of the very difficult figures, and to Mrs. B. Douglas for her conscientious job in preparing the manuscript.

#### REFERENCES

- 1. Estrin, G., "Organization of computer systems: the fixed plus variable structure computer," Proc. WJCC, 1960, 33-40.

- 2. Menabrea, L. F., "Statement of the Circumstances Attending the Invention and Construction of Mr. Babbage's Calculating Engines," Philosophical Magazine, Sept. 1848, p. 235.

- 3. Andrews, E. G., "The Bell Computer, Model VI," Annals of the Computation Laboratory of Harvard University, Harvard University Press, 1951, Vol. VI, pp 20-31.

- 4. Muller, D. E., "Asynchronous Switching Theory,"-Digital Computer Laboratory Report 243, University of Illinois, June, 1958.

- 5. Mann, M. F., Rathbone, R. R., and Bennett, J. B., "Whirlwind I Operation Logic," <u>Digital Computer Laboratory Report R-221</u>, Massachusetts Institute of Technology, May 1954, pp 3.16 3.18.

#### MACROMODULAR COMPUTER SYSTEMS

Technical Report No. 4

June 20, 1967

Computer Systems Laboratory

Washington University

St. Louis, Mo.

Reprints of a series of papers presented at the 1967 Spring Joint Computer Conference sponsored by the American Federation of Information Processing Societies at Atlantic City, April 19, 1967, as published in the Proceedings, Thompson Book Co., National Press Building, Washington, D.C. 2004. (Only the first three articles are reprinted here.)

The research reported in these papers was supported in part by the Information Processing Techniques Project of the Advanced Research Projects Agency under Contract SD-302, and by the Division of Research Facilities and Resources of the National Institutes of Health under grant FR-00218.

#### TABLE OF CONTENTS

|                                                                                                     |   | Page |

|-----------------------------------------------------------------------------------------------------|---|------|

| MACROMODULAR COMPUTER SYSTEMS Wesley A. Clark                                                       |   | 335  |

| A FUNCTIONAL DESCRIPTION OF MACROMODULES Severo M. Ornstein, Mishell J. Stucki, and Wesley A. Clark | • | 337  |

| LOGICAL DESIGN OF MACROMODULES  Mishell J. Stucki, Severo M. Ornstein, and Wesley A. Clark          | • | 357  |

# Macromodular computer systems

by WESLEY A. CLARK Chairman's Introduction Washington University St. Louis, Missouri

#### INTRODUCTION

The amount of logically irrelevent engineering detail inherent in the design and construction of a computer system is great. As a result, the task of creating a system based on the use of present techniques is so difficult and time-consuming that the number of different systems that can be put into use for evaluation and study by any one group of workers is small. This is unfortunate as we are thereby denied the opportunity to develop that insight into logical organization which can grow out of a working familiarity with many diverse forms. What is needed is a set of relatively simple, easily inter-connected modules from which working systems can be readily assembled for evaluation and study. With such a set, both the designer and user would be able to try out potentially powerful and novel structures on a very large scale, adjusting and improving the systems as needed. Once a design has been realized and its value established, it could then be reworked into tighter engineering form for maximum efficiency and for production by automatic wiring and fabrication techniques, and the experimental units made available for further studies or returned to "inventory" in the manner proposed by Estrin.1

The approach presented in the "following", papers describes modules which are primarily vehicles for experimental use and as such meet a set of requirements heretofore unnecessary in digital modules. Logical flexibility and ease of use are considered of primary importance while factors such as operating speed, economy, etc., are considered of secondary

importance. The requirements can be summarized as follows:

- (1) The modules must be functionally large enough to reduce logical detail by a significant amount and must be relatively easy to understand and assemble. The number of different types should be as small as possible so as to limit inventory, but at the same time, the set must be logically complete so that whole systems can be assembled. There must be not only central processor modules such as register and memory units, but also modules for power, signal conditioning, input-output buffering and control, together with a reasonable selection of input-output devices themselves.

- (2) The mode of combining units into larger structures must be very simple (a problem first considered by Babbage, who examined this matter "with unceasing anxiety" one hundred and twenty years ago).<sup>2</sup> The modules should be designed for easy mechanical assembly. Communication from one mechanical assemblage to another should be accomplished by means of easily connected cables.

- (3) All units should be designed so that the assembling of these units into a working system presents no logically irrelevant problems such as those relating to circuit loading, waveform deterioration, signal propagation delay, power supply interactions, and so forth, regardless of the size or complexity of the system. The modules should be powered and perhaps controlled individually, and all possible signal paths must be provided with signal-standardizing amplifiers capable of driving all possible loads.

We call units which meet these requirements macromodules to distinguish them from the more

<sup>\*</sup>This research was supported in part by the Advanced Research Projects Agency of the Department of Defense through contract SD-302 and by the Division of Research Facilities and Resources of the National Institutes of Health through grant FR-00218.

conventional computer system modules. In this report we present a set of macromodules which, although not "complete" in the above sense, meets all other requirements and is sufficient for the synthesis of all central processor functions of which we are presently aware.

The following papers present the principal direction, achievements, and goals of the macromodular computer development program under way at Washington University. They describe an approach in which flexibility and simplicity are brought to the forefront of factors relevant in computer design. Two aspects of this approach are distinguishable.

First, it adds an experimental element to the theoretical and simulational techniques now available to the system designer. Perhaps this can most effectively be employed in research groups having as their main objectives the creation of advanced computer systems for particular areas of work. Because of the relative ease with which a given configuration of macromodules can be profoundly altered, it is possible for such a group to work actively with several widely different forms in an attempt to find optimal configurations for different problem classes.

Second, it makes possible a smoothness of growth and refinement in an operating computing system. Because of the electronic independence of the macromodules, it is relatively easy to expand a macromodular system and to add new functions without seriously affecting the continuity of on-going work and without jeopardizing any existing investment in programs and operating procedures.

These properties of macromodular systems are of growing importance as we turn increasingly toward the user for new concepts in the search for more effective information processing systems.

#### REFERENCES

#### 1 G. ESTRIN

Organization of computer systems the fixed plus variable structure computer

Proc. WJCC 33-40 1960

#### 2 L. F. MENABREA

Statement of the circumstances attending the invention and construction of Mr. Babbage's calculating engines

Philosophical Magazine 235 September 1848

# A functional description of macromodules

by SEVERO M. ORNSTEIN, MISHELL J. STUCKI and WESLEY A. CLARK Washington University

St. Louis, Missouri

\*This research was supported in part by the Advanced Research Projects Agency of the Department of Defense through contract SD-302 and by the Division of Research Facilities and Resources of the National Institutes of Health through grant FR-00218.

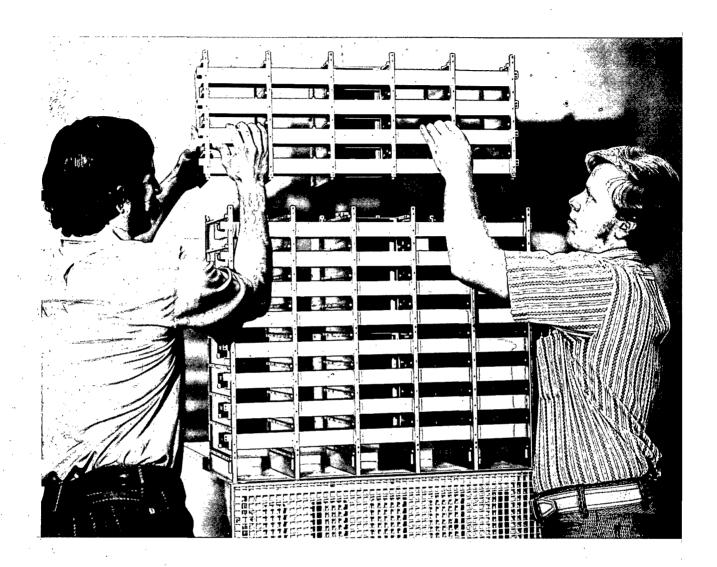

#### INTRODUCTION

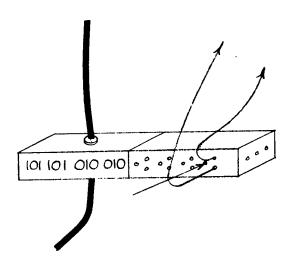

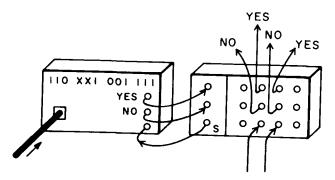

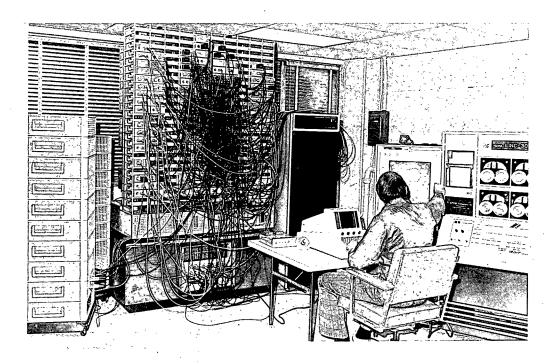

This paper describes a set of macromodular building blocks such as registers, adders, memories, control devices, etc., from which it is possible for the electronically-naive to construct arbitrarily large and complex computers that work. Machines are assembled by plugging the modules into cells of a special frame which provides for communication between adiacent cells. Explicit data pathways and control structures are then made by plugging in standardized cables. All pieces of a system are therefore recoverable and systems can be reconfigured easily. Data modules process twelve-bit word-segments; greater word lengths are obtained by interconnecting modules. Memory modules hold 4096 twelve-bit segments and can also be interconnected to form larger arrays. Particular attention is given to the problem of designing control structures. The control signals for a given process are routed along the cables of a control network whose topology is isomorphic to the flow diagram representing the process. The step from conception to realization can therefore be made directly.

The task of defining a set of macromodules or building blocks is not unlike that of defining an instruction repertoire for a computer. The fundamental requirement is that the set be sufficiently general to permit construction of any central processor.\* The particular set described here embodies this generality and satisfies the requirements set forth in another paper.' While it illustrates the approach we have taken, the set is by no means unique and, like a particular

instruction code, will be more convenient or efficient for some tasks than it will for others.

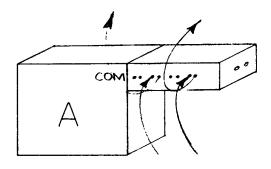

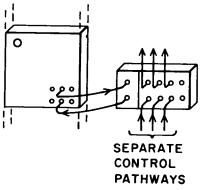

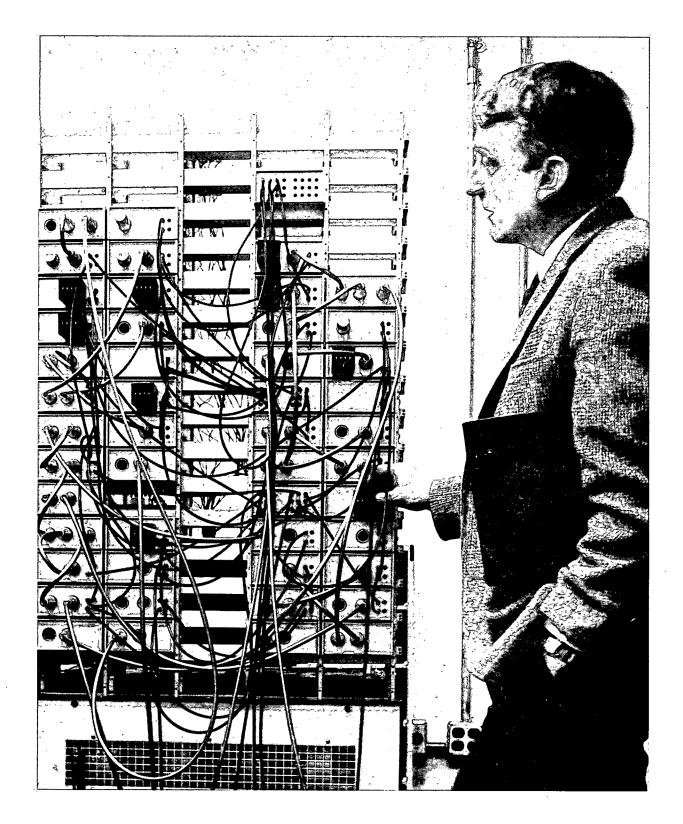

#### General characteristics

The macromodules to be described are relatively small, dimensionally modular boxes which plug into a cellular frame structure, some modules occupying more than one cell. Each module contains all of the electronic circuits and memory elements required in the performance of its particular function. Connectors on the frame provide for communication between modules in neighboring cells, and assemblages of units are thus made by plugging them into appropriately adjacent positions. Faceplates attached to the modules' front surfaces provide the electrical connectors for signal access, and standardized cables are provided for inter-assemblage communication. All connectors are backed by signal-standardizing amplifiers capable of driving any adjacent module or attachable cable. Since all cabling takes place between faceplates which are separable from the modules, it is possible to remove modules from a frame for temporary use elsewhere without disturbing the cabling.

Data processing modules are organized in parallel binary form with a word-length modulus of 12 bits, and are designed functionally for asynchronous operation. Memory modules hold 4096 12 bit words.†

The design of a system based on these modules requires, we believe, only the exercise of logic. The operability of the resulting system is not critically affected by the physical distribution or arrangement of

<sup>\*</sup>No input-output macromodules are discussed here although modules for various devices (scopes, tapes, printers, readers, etc.) are obviously required to complete the set.

<sup>†</sup>The numbers 12, 4096, and other such parameters have been made specific, for purposes of this paper, only to simplify description.

parts, the distances between units, the number or diversity of modules, or the routing of the interconnecting pathways. Macromodular systems are, as a result, capable of continuous growth and functional enrichment.

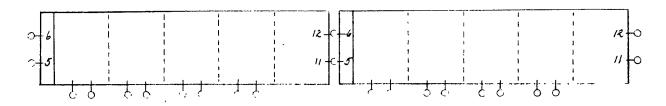

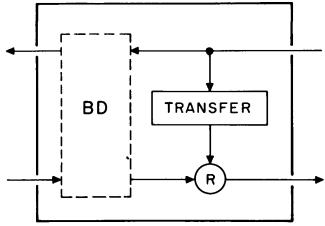

#### System organization

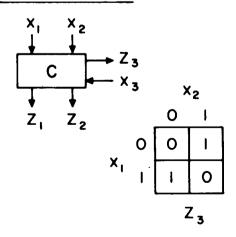

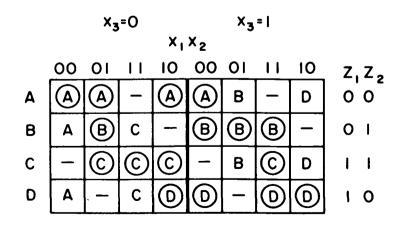

Macromodular systems may be viewed in terms of two logically distinct, interacting networks as shown in Figure 1. The processing network (the heavy-lined structure) consists of data processing elements interconnected by data pathways, and provides for the storage, propagation, and transformation of data within a system. The sequencing network (the light-lined structure) consists of control nodes distributed throughout the system, interconnected by control pathways. The structure of the processing network defines the basic data processing operations of the system while the structure of the sequencing network defines the order in which subsets of these basic operations can be carried out.

Interaction between these networks takes place at control terminals on the data processing elements. These terminals have two functions: )1) they allow the sequencing network to initiate operations, and (2) they return completion signals when the operations are finished. Each basic data processing operation has an associated set of these terminals (Figure 2), the number of terminals in the set being determined by the nature of the operation. Operations that manipulate data, data operations, have two, an initiation terminal and a completion terminal. Operations that check data for specific values, decision operations, have more than two, one of which initiates the opera-

Figure 1 - Processing and sequencing networks

Figure 2 – Data processing operations

tion while the others (completion terminals) indicate the value of the data found. Also shown in Figure 2 is a time continuous transformation element. This element, unlike those already described, performs its operation continuously. The data presented at its output changes directly in response to changes of input data rather than in response to control signals, and as a result, the element has no control terminals at all. An operation is initiated when a control signal arrives at an initiation terminal. The operation is executed and finally a control signal issues from the completion terminal and travels to the next control node in the sequencing network.

The order or sequence in which operations are performed is determined entirely by the structure of the sequencing network. This network is composed of signal nodes, calling elements, and interconnecting pathways. A signal node is an element which provides for the merging or branching of control signals data operations, have two, an initiation terminal and a completion terminal. Operations that check data for specific values, decision operations, have more than two, one of which initiates the operation while the others (completion terminals) indicate the value of the data found. Also shown in Figure 2 is a time continuous transformation element. This element, unlike those already described, performs its operation continuously. The data presented at its output changes directly in response to changes of input data rather than in response to control signals, and as a result, the element has no control terminals at all.

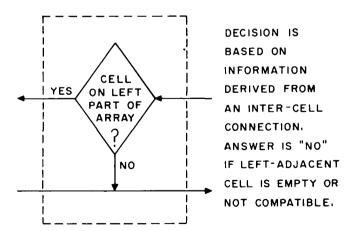

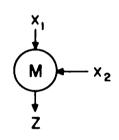

The order or sequence in which operations are performed is determined entirely by the structure of the sequencing network. This network is composed of signal nodes, calling elements, and interconnecting pathways. A *signal node* is an element which provides for the merging or branching of control signals. There are several types, two of which are shown in

Figure 3 - Control nodes

Figure 3. A calling element is one which, when activated by a control signal at its initiation terminal, causes an operation to take place and, when signaled of completion of the operation, produces its own completion signal in turn. An operation node is a calling element for data operations, and a decision node is a calling element for decision operations.

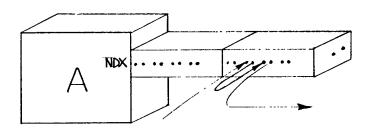

Control within a macromodular system is asynchronous, that is, each event in a sequence of events can be initiated by the completion signal from the preceding event. The simplest way of accomplishing this is to connect a cable from the completion terminal associated with each operation to the initiation terminal associated with the next operation. This scheme, though simple and effective, has the limitation that once the control terminals for an operation have been connected for one sequence, it is no longer possible to incorporate the operation into any other sequence. In such cases, rather than connect to the terminals associated with the operation, we connect instead to the terminals of a calling element associated with the operation, as shown in Figure 4. Since any number of calling elements may call the same operation, an operation may thus occur in as many distinct sequences as necessary. Figure 4 illustrates this for two different sequences, namely, the sequence z, y, x and the sequence z, x. Since both sequences include the operations z and x, they initiate the operations through calling elements. Calling elements are not needed for operation y, however, as it appears in only one sequence and can therefore be incorporated by connections directly to its control terminals.

The control elements and interconnections defining a given sequence are said to be the *control path* for

that sequence. The sequencing network is therefore the control path for the entire system.

#### Data validation

Whenever data values are used in either a data operation or a decision operation, it is necessary to be assured that 1) the results of all prior operations which could have perturbed the data are complete and 2) the new values of the data have propagated to the point of use regardless of the length of the pathway.

When information is used in the immediate locality of its source, i.e., within the same module, allowances for stabilization and signal progagation times are made within the module itself. When the source is remote from the point of use, a procedure known as data validation is followed to guarantee that the above two re-

Figure 4 - Example of sequence control

Figure 5 - Subsequence control

quirements are met. This process is discussed elsewhere.<sup>2</sup> For the present purposes, we shall assume that any attempt to use data following a perturbation of the data source will work properly, i.e. that the correct new value of the data will be used. Thus, there is no need for the designer to concern himself with details of propagation times so long as proper sequence is established.

#### The macromodules

We now proceed to give a functional description of the individual macromodules and illustrate their roles in various systems. Processing network elements are introduced first, and this is followed by a discussion of the various sequencing network elements. Power connections and the supporting frame structure are omitted from the figures to avoid obscuring the logical point being illustrated. A basic module type is sometimes fitted with more than one type of faceplate suiting it to different contexts. In such cases the circuits within the module sense the faceplate type and operation is suitably adjusted.

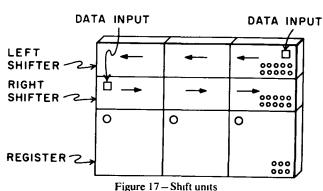

#### **Cables**